# Unveiling Thermal Effects on Sn-Doped $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diodes on Sapphire for High-Temperature Power Electronics

Manoj K. Yadav<sup>®</sup>, Arnab Mondal<sup>®</sup>, Satinder K. Sharma<sup>®</sup>, *Senior Member, IEEE*, and Ankush Bag<sup>(D)</sup>, *Member, IEEE*

Abstract—The study investigates the performance of Schottky barrier diodes (SBDs) fabricated on high-quality Sn-doped  $\beta$ -gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) film on sapphire (0006) substrate. Temperature-dependent performances are probed, in terms of forward and reverse bias characteristics. When temperature increases from 25 °C to 200 °C, the barrier height increases, and the ideality factor advances to unity. The current conduction happens differently at low and high temperatures because of the inhomogeneity in Schottky barrier height. Different methods are used to analyze temperature variations in the barrier heights. A high breakdown voltage of >200 V at 25 °C and a decent J<sub>ON</sub>/J<sub>OFF</sub> ratio for the all-temperature range are measured. The leakage current of the device does not significantly change with the temperature. These characteristics make the investigated Schottky diode structures on sapphire promising for future high-power electronics applications at elevated temperatures. Thus, costeffective integration of Ga<sub>2</sub>O<sub>3</sub> with non-native substrates is emphasized to enable rapid commercialization success.

Index Terms—Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), low-pressure chemical vapor deposition (LPCVD), sapphire, Schottky barrier diode (SBD), Sn doping.

# I. INTRODUCTION

**R** ECENTLY,  $\beta$ -gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) has been considered as a promising wide-bandgap semiconductor material for the next-generation power electronics, owing to its superior material properties, such as ultrawide-bandgap of 4.5-4.9 eV [1] compared with GaN (3.4 eV) and SiC

Manuscript received 30 August 2023; revised 5 November 2023; accepted 9 November 2023. This work was supported in part by the Centre for Design and Fabrication of Electronic Devices (C4DFED) IIT Mandi, Science and Engineering Research Board (SERB), Department of Science and Technology (DST), Government of India, under Grant ECR/2017/000810, and Grant CRG/2021/006815. The review of this article was arranged by Editor M. Buffolo. (Corresponding author: Manoj K. Yadav.)

Manoj K. Yadav is with the Institute of Sensor and Actuator Systems, TU Wien, 1040 Vienna, Austria (e-mail: manojyadav. iitmandi@gmail.com).

Arnab Mondal and Satinder K. Sharma are with the School of Computing and Electrical Engineering, IIT Mandi, Mandi 175005, India (e-mail: sunny.mondal2010@gmail.com; satinder@iitmandi.ac.in)

Ankush Bag is with the Department of Electronics and Electrical Engineering, IIT Guwahati, and Centre for Nanotechnology IIT Guwahati, Guwahati 781039, India (e-mail: bag.ankush@gmail.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2023.3333818.

Digital Object Identifier 10.1109/TED.2023.3333818

(3.2 eV), which enables a high theoretical breakdown field  $(E_c)$  of 8 MV/cm [2], [3], [4]. Consequently,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has a high Baliga's figure of merit (BFOM; defined as  $\varepsilon \mu E_c^3$ ) of 3444 [5], [6], which is more than three times higher than that of GaN and SiC [7], endorsing its proficiency, particularly for power electronics.

In the last few years, most researchers have used Ga<sub>2</sub>O<sub>3</sub> as a substrate to fabricate Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes (SBDs). However, due to the small wafer size and high cost of the  $Ga_2O_3$  substrate, the sapphire substrate could be a potential candidate for the deposition of Ga<sub>2</sub>O<sub>3</sub> film. Moreover, the poor thermal conductivity of Ga2O3 hinders its commercial use in a high-temperature regime leading to undesirable results [8], [9]. Indeed, the incorporation of a sapphire substrate in  $Ga_2O_3$ based power devices offers significant advantages, particularly in terms of enhancing heat dissipation efficiency. The higher thermal conductivity of sapphire enables it to effectively dissipate the heat generated during device operation at elevated temperatures. Consequently, this improved heat dissipation capability contributes to the overall reliability and performance of Ga<sub>2</sub>O<sub>3</sub>-based power devices under high-temperature conditions.

The ultrawide-bandgap of Ga2O3 allows for smaller device dimensions, leading to reduced power consumption losses. Impressive studies on Ga2O3 SBDs, MOSFETs, and MES-FETs have demonstrated high breakdown voltages and low ON-state resistances [2], [3], [10], [11], [13]. Limited studies have been conducted on Ga<sub>2</sub>O<sub>3</sub> on sapphire substrates, with a focus on optoelectronic applications [14], [15], [16], [17], [18], [19], [20]. However, Hu et al. [21] have fabricated  $Ga_2O_3$ nanomembrane on sapphire substrates for high-power applications, although the nanomembrane could be less promising for commercial applications considering scalability and reliability issues. Wang et al. [7] reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/TiN SBDs on heterogeneous integrated Ga<sub>2</sub>O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub>-Si substrate, studying their temperature-dependent electrical performance.

The next section describes the experimental details of device processing steps. Section III with results and discussions presents the material and electrical characteristics of the Ga<sub>2</sub>O<sub>3</sub> SBD where the overall performance of SBD has been probed and evaluated in terms of high-power response in the temperature range of 25 °C-200 °C. The last section refers the conclusion of this work.

0018-9383 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Authorized licensed use limited to: Indian Institute Of Technology (IIT) Mandi. Downloaded on November 23,2023 at 07:00:57 UTC from IEEE Xplore. Restrictions apply.

## **II. EXPERIMENTAL DETAIL**

The Sn-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film was grown on *c*-plane sapphire substrate using the low-pressure chemical vapor deposition (LPCVD) technique. Before deposition, the sapphire wafer underwent cleaning with acetone and isopropyl alcohol for 5 min. Inside a quartz boat, 100 mg of Ga metal and 20 mg of Sn metal were positioned, while the substrate was placed on a separate quartz boat and loaded into the tube furnace. The substrate temperature was maintained at 1050 °C, and the base pressure and processing pressure of the furnace were  $5 \times 10^{-2}$  and 1 mbar, respectively. The thin-film deposition was carried out for 1 h. Material characteristics of the thin film have been carried out using X-ray diffraction (XRD), fieldemission scanning electron microscope (FESEM), and atomic force microscopy (AFM). Doping concentration and mobility of samples have been determined using the Hall technique.

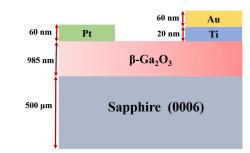

To fabricate lateral SBDs, Pt (60 nm) and Ti/Au (20/60 nm) layers were sputtered on the top of the Ga<sub>2</sub>O<sub>3</sub> film to form the Schottky and ohmic contacts, respectively. The schematic of the fabricated device structure is illustrated in Fig. 1, with a distance of 418.30  $\mu$ m between Pt and Ti/Au contacts. Electrical characteristics of the Pt/Ga<sub>2</sub>O<sub>3</sub> SBD structures were investigated over a temperature range of 25 °C–200 °C, with measurements taken at interval of 25 °C using a Keithley 4200 semiconductor measuring unit. The temperature dependence study was performed using the LINKAM LTS420E heating stage.

# **III. RESULTS AND DISCUSSION**

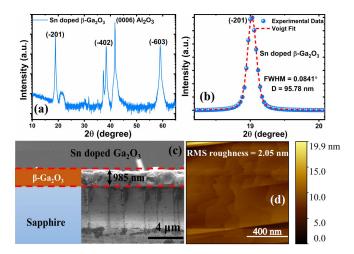

In Fig. 2(a), XRD pattern of the sample confirms that a high crystalline quality  $Ga_2O_3$  film with  $\beta$  phase was deposited on sapphire substrate. The dominant planes are (-201) of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and (0006) of sapphire. The (-402) and (-603) planes are fundamentally higher order diffraction of the (-201) plane. The peak at  $21^{\circ}$  is from the (0003) plane of the sapphire substrates. A peak around 37° has also been observed, which might be the (401) plane of Ga<sub>2</sub>O<sub>3</sub> as given in JCPDS 01-076-0673, observed for all the samples. The fullwidth half-maxima (FWHM) of 0.0841° has been obtained using Voigt fitting of the (-201) plane, as shown in Fig. 2(b). The average crystallite size (D) is determined using the Scherrer formula. The measured value of D was  $\sim$ 95.78 nm. The small FWHM and large crystallite size signify the high crystalline quality of the film. Thereby, XRD results reveal the single-phase crystalline nature of the Ga<sub>2</sub>O<sub>3</sub> film deposited on sapphire. A film thickness of 985 nm for the Sn-doped Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> sample is confirmed by cross-sectional FESEM, as shown in Fig. 2(c). A thicker layer can improve the overall surface flatness and reduce roughness. The interface roughness is an important factor in determining the performance of devices, especially in SBDs. The AFM technique was used to determine the topology of the film surface. A root-meansquare (rms) roughness of  $\sim 2$  nm was measured, as shown in Fig. 2(d). Typical step-flow dominating surface morphology has been observed. The Sn-doped Ga<sub>2</sub>O<sub>3</sub> film has net-doping concentration and mobility of  $3 \times 10^{17}$  cm<sup>-3</sup> and 4 cm<sup>2</sup>/V·s, respectively, measured at room temperature using the standard Hall method.

Fig. 1. Schematic (not in scale) of lateral Pt SBDs on  $Ga_2O_3$  layer with the approximate dimensions of each layer.

Fig. 2. (a) XRD pattern of the  $Ga_2O_3/Al_2O_3$  sample. (b) XRD pattern to measure FWHM and crystallite size using (-201) plane of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. (c) Cross-sectional FESEM image. (d) AFM image of the Ga<sub>2</sub>O<sub>3</sub> surface.

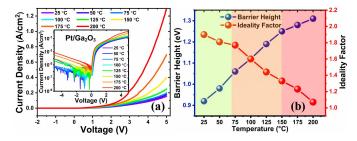

Fig. 3(a) depicts temperature-dependent current density versus voltage (J-V) characteristics of Pt/Ga<sub>2</sub>O<sub>3</sub> SBDs in both linear and semilogarithmic scale. At low forward bias, the J-V behavior is linear, as shown in Fig. 3(a). However, higher forward bias reveals deviation, likely due to significant effect of series resistance [22]. Typically, thermionic emission is the dominant current conduction mechanism at high temperatures [7]. Hence, the current density increases, as the temperatures increases from 25 °C to 200 °C at the same forward bias [Fig. 3(a)]. The reverse bias nonsaturation behavior could stem from image force barrier lowering [23] and Schottky barrier height inhomogeneity [22], [24], [25]. The J-V characteristics based on the thermionic emission theory considering series resistance can be described by the following relation [26], [27]:

$$J = J_0 \left[ \exp\left(\frac{q(V - JAR_S)}{\eta kT}\right) - 1 \right]$$

(1)

$$J_0 = A^* T^2 \exp\left(\frac{-q\phi_B}{kT}\right) \tag{2}$$

where  $J_0$  is the saturation current density,  $\eta$  is the ideality factor, q is the free electron charge, k is Boltzmann's constant, A is the diode area,  $A^*$  is the Richardson constant,  $\phi_B$  is the barrier height,  $R_S$  is the series resistance, and T is the temperature at which the device is operating. Here, image force barrier lowering could be neglected, because it is a weak function of applied voltage [25]. It is also observed that  $J_0$  increases with an increase in temperature, and the

Fig. 3. (a) Linear and semilogarithmic scale J-V characteristics of Pt/Ga<sub>2</sub>O<sub>3</sub> SBD in the temperature range of 25 °C–200 °C. (b) Temperature dependence of barrier height and ideality factor extracted from J-V characteristics of SBD. In the figure, yellow green, orange, and red colors indicate the mild-, moderate-, and high-temperature regions, respectively.

value of  $J_0$  varies from 2.58  $\times$  10<sup>-7</sup> A/cm<sup>2</sup> (at 25 °C) to 2.01  $\times$  10<sup>-5</sup> A/cm<sup>2</sup> (at 200 °C). In the investigation of SBDs, the ideality factor is a crucial parameter measured using J-V characteristics. A desirable  $\eta$  value of 1.90 at 25 °C is obtained for SBD. Barrier height of the diode can be determined using (2). As temperature varies from 25 °C to 200 °C,  $\phi_B$  increases from 0.92 to 1.31 eV, while  $\eta$  decreases from 1.90 to 1.07, as shown in Fig. 3(b). This temperature-dependent trend indicates a strong influence of temperature on  $\phi_B$  and  $\eta$ . This behavior could be attributed to the unevenness of Schottky surface in SBDs [28]. The presence of barrier height inhomogeneity could result from the nonepitaxial deposition of Schottky contacts on the semiconductor surface, leading to a rough metal-semiconductor (MS) interface [29]. Another possible reason might be due to the difference in thermal expansion coefficients between the materials involved [30]. The other reasons for barrier inhomogeneity in the Schottky diodes could be vacancy-related defects, surface and bulk defects, and variation in the electric field at the MS interface due to dislocations [24], [31], [32]. Surface and bulk defects in Ga<sub>2</sub>O<sub>3</sub> Schottky diodes introduce energy levels and affect charge carrier trapping and emission in a temperature-dependent manner. These defects can lead to temperature-sensitive inhomogeneities in the Schottky barrier height [33]. Dislocations in the Ga<sub>2</sub>O<sub>3</sub> material can cause localized variations in the electric field at the MS interface. These dislocations can create regions with altered electrical properties, including changes in carrier concentration and mobility, which affect the electric field. These variations are temperature-sensitive and can result in inhomogeneities in device performance [34].

Theoretically, the MS interface should be flat and uniform according to thermionic emission theory. However, there is the existence of locally nonuniform regions having lower and higher barrier height patches on very small scales in an inhomogeneous Schottky barrier surface. This leads to uneven current conduction at the MS interface across different temperatures. At lower temperatures, conduction occurs through charge carriers crossing lower barrier height patches, while at higher temperatures, conduction involves charge carriers crossing relatively higher barrier patches. Consequently, current increases with rising temperatures. At 200 °C,  $\eta$  approaches unity, indicating a thermionic emission behavior. The  $\phi_B$  value

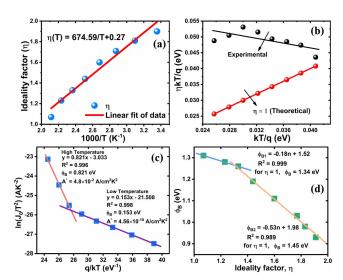

Fig. 4. (a) Plot of ideality factor versus 1000/T. (b) Plot of  $\eta kT/q$  versus kT/q. (c)  $\ln(J_0)$  versus q/kT plot. (d)  $\phi_B$  versus  $\eta$  plot to verify the barrier height inhomogeneity in the lateral Pt/Ga<sub>2</sub>O<sub>3</sub> SBD.

(1.31 eV) at this temperature aligns closely with the theoretical barrier height of Pt/Ga<sub>2</sub>O<sub>3</sub> diodes.

The variation in ideality factor with temperature was found to change in linearity with temperature, as shown in Fig. 4(a)

$$\eta(T) = n_k + \frac{T_k}{T} \tag{3}$$

where  $n_k$  and  $T_k$  are constant having the values of 0.27 and 674.59 K, respectively. The high value of ideality factor at lower temperatures may be attributed to the existence of image force lowering, barrier inhomogeneity at the MS interface, and interface states [22], [24], [25], [29], [35].

Furthermore, the temperature-dependent ideality factor was further investigated to explain the primary transport mechanisms by plotting  $\eta kT/q$  versus kT/q. The plot of  $\eta kT/q$ versus kT/q is shown in Fig. 4(b), which illustrates the theoretical along with the experimental results in the plot. It is clear that there is a relationship between the theoretical and experimental curves of the SBD. In this plot, the straight line fit to the experimental values should be parallel to the line of theoretical values [36]. However, as shown in Fig. 4(b), the straight line fit to the experimental data is not parallel to the theoretical data line. Thus, the fabricated SBD does not follow the ideal Schottky diode behavior.

In order to further investigate the barrier height inhomogeneity, a robust and extensively validated technique has been used—the Richardson plot of saturation current density [36]. Equation (2) of reverse saturation current density can be expressed as follows:

$$\ln\left(\frac{J_0}{T^2}\right) = \ln(A^*) - \frac{q\phi_B}{kT}.$$

(4)

The Richardson plot of  $\ln(J_0)$  versus q/kT has two different linear regions with different slopes and intercepts, as shown in Fig. 4(c). This type of behavior of the Richardson plot is attributed to the inhomogeneous Schottky barrier heights [37]. In the first region, at high temperatures, the values of Richardson constant ( $A^*$ ) and activation energy ( $E_a = \phi_B$ ) were extracted from the intercept and slope of the straight line

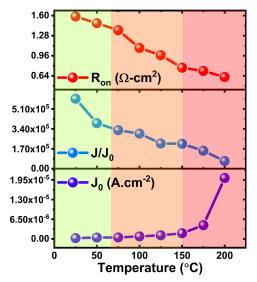

Fig. 5. Variation of  $J_0$ ,  $(J/J_0)$ , and  $R_{ON}$  with the temperature increases from 25 °C to 200 °C. In the figure, yellow green, orange, and red colors indicate the mild-, moderate-, and high-temperature regions, respectively.

as  $4.8 \times 10^{-2}$  A/cm<sup>2</sup>K<sup>2</sup> and 0.821 eV, respectively, Whereas, in the second region, at low temperatures, the values of  $A^*$  and  $E_a$  were found to be  $4.56 \times 10^{-10}$  A/cm<sup>2</sup>K<sup>2</sup> and 0.153 eV, respectively. The  $A^*$  notably differs from Ga<sub>2</sub>O<sub>3</sub> theoretical value (41.1 A/cm<sup>2</sup>K<sup>2</sup>), implying a shift from thermionic emission theory, possibly toward thermionic field emission. The ln( $J_0$ ) versus q/kT plot underscores distinct barrier heights and Richardson constants, pinpointing inhomogeneous barrier heights at the Schottky interface. This gives rise to elevated ideality factors at lower temperatures [24], [36]. Furthermore, this investigation is supporting the previous observation on barrier height inhomogeneity.

To corroborate the effectiveness of the previously employed methodologies for evaluating barrier height inhomogeneity within Schottky diodes, an additional investigation was conducted. This technique enhances our technical understanding and rigorously validates our assessment of the diode's barrier height variations. Fig. 4(d) shows the plot of temperature-dependent barrier height versus ideality factor. It reveals two distinct barrier heights and a linear correlation between barrier height and ideality factor. Extrapolation at  $\eta = 1$  yields 1.34 eV in one region and 1.45 eV in another, highlighting barrier height inconsistency at the MS junction. High values ideality factor at low temperatures are attributed to this barrier height inhomogeneity, consistent with findings by Schmitsdorf et al. [38], who linked it to lateral inhomogeneities in the barrier heights. Thus, the high ideality factor at low temperatures primarily results from this barrier height inhomogeneity.

The variations in  $J_0$ ,  $(J/J_0)$ , and  $R_{\rm ON}$  with the temperature are shown in Fig. 5. The specific ON-state resistance  $(R_{\rm ON})$ decreases from 1.585  $\Omega \cdot \rm{cm}^2$  (at 25 °C) to 0.621  $\Omega \cdot \rm{cm}^2$  (at 200 °C) for the Pt/Ga<sub>2</sub>O<sub>3</sub>, which has been measured from the slope of the fitting line to the temperature-dependent J-V characteristics. Poor mobility may be the reason for this relatively high  $R_{\rm ON}$ . The current density ON/OFF ratio  $(J_{\rm ON}/J_{\rm OFF})$  decreases, as the temperature increases from

Fig. 6. Semilogarithmic and linear scale reverse -V characteristics in the temperature range of 25 °C–200 °C.

T = 25 °C to 200 °C. However, the lateral SBD has a decent  $J_{\rm ON}/J_{\rm OFF}$  ratio even at a high temperature of 200 °C.

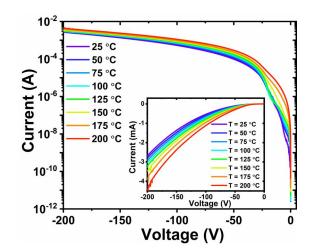

Fig. 6 shows the reverse current-voltage (I-V) characteristics of the lateral Ga<sub>2</sub>O<sub>3</sub> SBD across the temperature range of 25 °C-200 °C. Notably, no breakdown of the device is observed up to 200 V. Given the instrument's operational limits, we cannot surpass this voltage, implying that the device breakdown voltage exceeds the recorded value. The current values at -200 V are  $\sim 2.8 \times 10^{-3}$  to  $\sim 4.8 \times 10^{-3}$  A for the T = 25 °C-200 °C, respectively. It is observed that there is no significant difference in the current value at a high reverse voltage (200 V) across various temperatures. The temperature effect is more prominent at low reverse voltages where thermal energy plays a significant role, while at high reverse voltages, field emission becomes the dominant mechanism, reducing the impact of temperature on leakage current [39]. This suggests that higher temperature does not notably affect leakage current of the lateral device.

Table I presents a comprehensive comparison between the previously reported lateral and vertical  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device structures fabricated on sapphire substrates and the current research findings. While there are limited published reports available regarding  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBDs fabricated on sapphire substrates, it is noteworthy that the growth of the epilayer has been performed using various methods, resulting in distinct epilayer structures. These discrepancies in growth techniques and epilayer structures necessitate a careful examination and comparison in order to ascertain the impact of these variations on the overall device performance and characteristics.

Among the assortment of cited works detailed in Table I, our study presents a unique opportunity to conduct a highly precise and comprehensive comparison with the research conducted by Sood et al. [40]. This is primarily attributed to the remarkable similarity observed in terms of both epilayer and device structures. However, it is important to acknowledge that divergences exist in the growth method and doping material employed. Sood et al. [40] have reported Si-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> lateral SBDs in the year of 2023. In their study, they deposited Si-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film onto a sapphire substrate using a metal–organic chemical vapor deposition

| VARIOUS REPORTED p-GA2O3 DEVICE STRUCTURES ON SAPPHIRE SUBSTRATES AS COMPARED WITH THIS WORK |                       |                  |          |                       |        |               |                                                    |                       |            |

|----------------------------------------------------------------------------------------------|-----------------------|------------------|----------|-----------------------|--------|---------------|----------------------------------------------------|-----------------------|------------|

| Device<br>Structure                                                                          | Epilayer<br>Structure | Growth<br>Method | Doping   | Epilayer<br>Thickness | $\eta$ | $\phi_B$ (eV) | $\mathbf{R}_{on}$<br>( $\Omega$ -cm <sup>2</sup> ) | $\mathbf{V}_{BR}$ (V) | References |

| L-SBDs                                                                                       | Thin film             | LPCVD            | Sn-doped | 985 nm                | 1.07   | 1.31          | 0.62                                               | > 200                 | This work  |

| L-SBDs                                                                                       | Thin film             | MOCVD            | Si-doped | 210 nm                | 1.97   | 0.54          | 0.81                                               | 370                   | [40]       |

| L-MISD                                                                                       | Thin film             | MOCVD            | Si-doped | 210 nm                | 1.61   | -             | 1.92                                               | 309                   | [41]       |

| MOSFET                                                                                       | Thin film             | MOCVD            | Si-doped | 150 nm                | -      | -             | -                                                  | 360                   | [42]       |

| MOSFET                                                                                       | Thin film             | MOCVD            | Si-doped | 150 nm                | -      | -             | -                                                  | 400                   | [43]       |

| V-SBDs                                                                                       | Flakes                | Exfoliation      | -        | $10 \ \mu m$          | 1.17   | 1.30          | 0.005                                              | 172                   | [44]       |

| L-SBDs                                                                                       | Nano-membrane         | Exfoliation      | Sn-doped | 400 nm                | -      | -             | .05                                                | 1700                  | [21]       |

| MOSFET                                                                                       | Nano-membrane         | Exfoliation      | -        | 190 nm                | -      | -             | 0.0074                                             | 800                   | [45]       |

TABLE I

VARIOUS REPORTED &-GA2O3 DEVICE STRUCTURES ON SAPPHIRE SUBSTRATES AS COMPARED WITH THIS WORK

(MOCVD) technique. Their experimental results revealed a  $V_{\rm BR}$  of 370 V, an  $R_{\rm ON}$  of 0.81  $\Omega \cdot \rm cm^2$ , an  $\eta$  of 1.97, and a  $\phi_B$  of 0.54 eV for the lateral SBDs.

Present work demonstrates superior device performance characteristics, specifically a lower  $R_{\rm ON}$  and  $\eta$ , indicating improved conductivity and more efficient charge transport. In addition, our research reveals a higher barrier height, indicating enhanced energy barrier for carrier injection and reduced leakage current. Moreover, our estimations indicate that the  $V_{\rm BR}$  is much greater than 200 V because of low leakage current. Furthermore, our devices exhibit stable dc responses even under high-temperature conditions.

Thus, this study focuses on the growth of Sn-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films on sapphire substrates using the LPCVD technique. The fabricated SBDs exhibited commendable performance, particularly in high-temperature and high-power applications. Moreover, the enhancement of device performance for high-power applications can be achieved through the utilization of diverse device structures. However, it should be noted that these alternate structures require meticulous consideration and evaluation to ensure their compatibility and effectiveness in meeting the desired power requirements.

#### **IV. CONCLUSION**

In this study, Sn-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBDs were fabricated on sapphire using LPCVD. Pt/Ga<sub>2</sub>O<sub>3</sub> devices were characterized from 25 °C to 200 °C. The SBD exhibited excellent static and dynamic characteristics, including low saturation current density, low ideality factor, high barrier height, and good  $J_{\rm ON}/J_{\rm OFF}$  ratio. As temperature increased, the barrier height rose, and ideality factor decreased. The ideality factor reaching close to unity at 200 °C and barrier height approaching the theoretical value. The current conduction mechanism changed with temperature due to the inhomogeneous barrier heights. This inhomogeneity in barrier height led to significantly high ideality factors at low temperatures, as evident from the results of various plots. SBD had >200 breakdown voltage, consistent leakage current across temperatures. The stable performance at high temperatures may be attributed to the higher thermal conductivity of the sapphire substrate compared with  $Ga_2O_3$ . Thus, this fabricated Sn-doped  $\beta$ - $Ga_2O_3$  SBD on sapphire demonstrates great potential for high-power and high-temperature applications.

### REFERENCES

- M. K. Yadav, A. Mondal, S. Das, S. K. Sharma, and A. Bag, "Impact of annealing temperature on band-alignment of PLD grown Ga<sub>2</sub>O<sub>3</sub>/Si (100) heterointerface," *J. Alloys Compounds*, vol. 819, Apr. 2020, Art. no. 153052, doi: 10.1016/j.jallcom.2019.153052.

- [2] M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs with a breakdown voltage of over 750 V," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 212–215, Feb. 2016, doi: 10.1109/LED.2015.2512279.

- [3] K. Sasaki, M. Higashiwaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes fabricated by using single-crystal β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates," *IEEE Electron Device Lett.*, vol. 34, no. 4, pp. 493–495, Apr. 2013, doi: 10.1109/LED.2013.2244057.

- [4] M. K. Yadav, A. Mondal, S. K. Sharma, and A. Bag, "Probing interface trapping characteristics of Au/β-Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diode on Si (100)," *IEEE Trans. Device Mater. Rel.*, vol. 21, no. 4, pp. 613–619, Dec. 2021, doi: 10.1109/TDMR.2021.3125244.

- [5] H. Zhou, S. Alghmadi, M. Si, G. Qiu, and D. Y. Peide, "Al<sub>2</sub>O<sub>3</sub>/β-Ga<sub>2</sub>O<sub>3</sub> (-201) interface improvement through piranha pretreatment and postdeposition annealing," *IEEE Electron Device Lett.*, vol. 37, no. 11, pp. 1411–1414, 2016, doi: 10.1109/LED.2016.2609202.

- [6] M. K. Yadav, A. Mondal, S. Shringi, S. K. Sharma, and A. Bag, "Performance enhancement of β-Ga<sub>2</sub>O<sub>3</sub> on Si (100) based Schottky barrier diodes using reduced surface field," *Semicond. Sci. Technol.*, vol. 35, no. 8, Aug. 2020, Art. no. 085009, doi: 10.1088/1361-6641/ab8e64.

- [7] Y. Wang et al., "Temperature-dependent characteristics of Schottky barrier diode on heterogeneous β-Ga<sub>2</sub>O<sub>3</sub> (201)-Al<sub>2</sub>O<sub>3</sub>-Si substrate," *J. Phys. D, Appl. Phys.*, vol. 54, no. 3, 2020, Art. no. 034004, doi: 10.1088/1361-6463/abbeb2.

- [8] M. Slomski, N. Blumenschein, P. P. Paskov, J. F. Muth, and T. Paskova, "Anisotropic thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub> at elevated temperatures: Effect of Sn and Fe dopants," *J. Appl. Phys.*, vol. 121, no. 23, Jun. 2017, Art. no. 235104, doi: 10.1063/1.4986478.

- [9] M. Handwerg, R. Mitdank, Z. Galazka, and S. F. Fischer, "Temperaturedependent thermal conductivity in Mg-doped and undoped β-Ga<sub>2</sub>O<sub>3</sub> bulk-crystals," *Semicond. Sci. Technol.*, vol. 30, no. 2, Feb. 2015, Art. no. 024006, doi: 10.1088/0268-1242/30/2/024006.

- [10] M. K. Yadav, A. Mondal, S. Kumar, S. K. Sharma, and A. Bag, "Integration of β-Ga<sub>2</sub>O<sub>3</sub> on Si (100) for lateral Schottky barrier diodes," in *Proc. IEEE 8th Workshop Wide Bandgap Power Devices Appl. (WiPDA)*, Nov. 2021, pp. 263–267, doi: 10.1109/WiPDA49284.2021.9645081.

- [11] M. Higashiwaki et al., "Depletion-mode  $Ga_2O_3$  metal-oxidesemiconductor field-effect transistors on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrates and temperature dependence of their device characteristics," *Appl. Phys. Lett.*, vol. 103, no. 12, Sep. 2013, Art. no. 123511, doi: 10.1063/1.4821858.

- [12] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Development of gallium oxide power devices," *Phys. Status Solidi* (A), vol. 211, no. 1, pp. 21–26, Jan. 2014, doi: 10.1002/pssa.201330197.

- [13] K. D. Chabak et al., "Enhancement-mode Ga<sub>2</sub>O<sub>3</sub> wrap-gate fin field-effect transistors on native (100)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate with high breakdown voltage," *Appl. Phys. Lett.*, vol. 109, no. 21, Nov. 2016, Art. no. 213501, doi: 10.1063/1.4967931.

- [14] Y. An et al., "Epitaxial growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films on Ga<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> substrates by using pulsed laser deposition," *J. Adv. Dielectr.*, vol. 9, no. 4, Aug. 2019, Art. no. 1950032, doi: 10.1142/s2010135x19500322.

- [15] A. Mondal, S. Nandi, M. K. Yadav, A. Nandi, and A. Bag, "Broad range (254–302 nm) and high performance Ga<sub>2</sub>O<sub>3</sub>:SnO<sub>2</sub> based deep UV photodetector," *IEEE Trans. Nanotechnol.*, vol. 21, pp. 320–327, 2022, doi: 10.1109/TNANO.2022.3186472.

- [16] C. Hu, F. Zhang, K. Saito, T. Tanaka, and Q. Guo, "Low temperature growth of Ga<sub>2</sub>O<sub>3</sub> films on sapphire substrates by plasma assisted pulsed laser deposition," *AIP Adv.*, vol. 9, no. 8, Aug. 2019, Art. no. 085022, doi: 10.1063/1.5118700.

- [17] J. Wei et al., "β-Ga<sub>2</sub>O<sub>3</sub> thin film grown on sapphire substrate by plasmaassisted molecular beam epitaxy," J. Semicond., vol. 40, no. 1, Jan. 2019, Art. no. 012802, doi: 10.1088/1674-4926/40/1/012802.

- [18] A. Mondal, M. K. Yadav, and A. Bag, "Transition from thin film to nanostructure in low pressure chemical vapor deposition growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>: Impact of metal gallium source," *Thin Solid Films*, vol. 709, Sep. 2020, Art. no. 138234, doi: 10.1016/j.tsf.2020.138234.

- [19] X. Liu, Q. Liu, B. Zhao, Y. Ren, B. W. Tao, and W. L. Zhang, "Comparison of β-Ga<sub>2</sub>O<sub>3</sub> thin films grown on r-plane and c-plane sapphire substrates," *Vacuum*, vol. 178, Aug. 2020, Art. no. 109435, doi: 10.1016/j.vacuum.2020.109435.

- [20] A. Mondal, M. K. Yadav, S. Shringi, and A. Bag, "Extremely low dark current and detection range extension of Ga<sub>2</sub>O<sub>3</sub> UV photodetector using Sn alloyed nanostructures," *Nanotechnology*, vol. 31, no. 29, May 2020, Art. no. 294002, doi: 10.1088/1361-6528/ab82d4.

- [21] Z. Hu et al., "Lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diode on sapphire substrate with reverse blocking voltage of 1.7 kV," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 815–820, 2018, doi: 10.1109/JEDS.2018. 2853615.

- [22] P. Chattopadhyay and D. Haldar, "The DC characteristics of anisotype heterojunction in the presence of interface states and series resistance," *Appl. Surf. Sci.*, vol. 143, nos. 1–4, pp. 287–300, 1999, doi: 10.1016/S0169-4332(98)00907-6.

- [23] A. Kaya, S. Demirezen, H. Tecimer, and S. Altindal, "Temperature and voltage effect on barrier height and ideality factor in Au/PVC + TCNQ/p-Si structures," *Adv. Polym. Technol.*, vol. 33, no. S1, May 2014, Art. no. 21442, doi: 10.1002/adv.21442.

- [24] R. T. Tung, "Electron transport at metal-semiconductor interfaces: General theory," *Phys. Rev. B*, vol. 45, no. 23, pp. 13509–13523, Jun. 1992, doi: 10.1103/physrevb.45.13509.

- [25] S. M. Sze, Semiconductor Devices: Physics and Technology. Hoboken, NJ, USA: Wiley, 2008.

- [26] M. K. Yadav, S. K. Sharma, and A. Bag, "Evaluation of diode characteristics for fully vertical β-Ga<sub>2</sub>O<sub>3</sub> on silicon (100) substrate," *J. Mater. Sci., Mater. Electron.*, vol. 31, no. 16, pp. 13845–13856, Aug. 2020, doi: 10.1007/s10854-020-03944-0.

- [27] M. K. Yadav, A. Mondal, S. K. Sharma, and A. Bag, "Substrate orientation dependent current transport mechanisms in β-Ga<sub>2</sub>O<sub>3</sub>/Si based Schottky barrier diodes," *J. Vac. Sci. Technol. A, Vac., Surf., Films*, vol. 39, no. 3, May 2021, Art. no. 033203, doi: 10.1116/6.0000858.

- [28] H. Sheoran, B. R. Tak, N. Manikanthababu, and R. Singh, "Temperaturedependent electrical characteristics of Ni/Au vertical Schottky barrier diodes on β-Ga<sub>2</sub>O<sub>3</sub> epilayers," *ECS J. Solid State Sci. Technol.*, vol. 9, no. 5, Jan. 2020, Art. no. 055004, doi: 10.1149/2162-8777/ab96ad.

- [29] J. H. Werner and H. H. Guttler, "Barrier inhomogeneities at Schottky contacts," J. Appl. Phys., vol. 69, no. 3, pp. 1522–1533, Feb. 1991, doi: 10.1063/1.347243.

- [30] S. Toumi, A. Ferhat-Hamida, L. Boussouar, A. Sellai, Z. Ouennoughi, and H. Ryssel, "Gaussian distribution of inhomogeneous barrier height in tungsten/4H-SiC (000–1) Schottky diodes," *Microelectronic Eng.*, vol. 86, no. 3, pp. 303–309, Mar. 2009, doi: 10.1016/j.mee.2008.10.015.

- [31] R. T. Tung, "The physics and chemistry of the Schottky barrier height," *Appl. Phys. Rev.*, vol. 1, no. 1, Mar. 2014, Art. no. 011304, doi: 10.1063/1.4858400.

- [32] W. Mönch, "Barrier heights of real Schottky contacts explained by metal-induced gap states and lateral inhomogeneities," *J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct. Process., Meas., Phenomena*, vol. 17, no. 4, pp. 1867–1876, Jul. 1999, doi: 10.1116/1.590839.

- [33] J. Shi et al., "Thermal transport across metal/β-Ga<sub>2</sub>O<sub>3</sub> interfaces," ACS Appl. Mater. Interfaces, vol. 13, no. 24, pp. 29083–29091, Jun. 2021, doi: 10.1021/acsami.1c05191.

- [34] A. Jayawardena, A. C. Ahyi, and S. Dhar, "Analysis of temperature dependent forward characteristics of Ni/β-Ga<sub>2</sub>O<sub>3</sub> Schottky diodes," *Semicond. Sci. Technol.*, vol. 31, no. 11, 2016, Art. no. 115002, doi: 10.1088/0268-1242/31/11/115002.

- [35] R. Hackam and P. Harrop, "Electrical properties of nickel-low-doped n-type gallium arsenide Schottky-barrier diodes," *IEEE Trans. Electron Devices*, vol. ED-19, no. 12, pp. 1231–1238, Dec. 1972, doi: 10.1109/ted.1972.17586.

- [36] F. Iucolano, F. Roccaforte, F. Giannazzo, and V. Raineri, "Barrier inhomogeneity and electrical properties of Pt/GaN Schottky contacts," *J. Appl. Phys.*, vol. 102, no. 11, Dec. 2007, Art. no. 113701, doi: 10.1063/1.2817647.

- [37] A. F. Özdemir, A. Turut, and A. Kökçe, "The double Gaussian distribution of barrier heights in Au/n-GaAs Schottky diodes from I–V–T characteristics," *Semicond. Sci. Technol.*, vol. 21, no. 3, pp. 298–302, Mar. 2006, doi: 10.1088/0268-1242/21/3/016.

- [38] R. Schmitsdorf, T. Kampen, and W. Mönch, "Correlation between barrier height and interface structure of AgSi (111) Schottky diodes," *Surf. Sci.*, vol. 324, nos. 2–3, pp. 249–256, 1995, doi: 10.1016/0039-6028(94)00791-8.

- [39] D. Neamen, Semiconductor Physics and Devices. New York, NY, USA: McGraw-Hill, 2002.

- [40] A. Sood et al., "Electrical performance study of Schottky barrier diodes using ion implanted β-Ga<sub>2</sub>O<sub>3</sub> epilayers grown on sapphire substrates," *Mater. Today Adv.*, vol. 17, Mar. 2023, Art. no. 100346, doi: 10.1016/j.mtadv.2023.100346.

- [41] R.-H. Horng et al., "Metal-insulator-semiconductor type diode based on implanted β-Ga<sub>2</sub>O<sub>3</sub> epilayers grown on sapphire substrate by metalorganic chemical vapor deposition," *Mater. Today Adv.*, vol. 18, Jun. 2023, Art. no. 100382, doi: 10.1016/j.mtadv.2023.100382.

- [42] J.-H. Park, R. McClintock, and M. Razeghi, "Ga<sub>2</sub>O<sub>3</sub> metal-oxidesemiconductor field effect transistors on sapphire substrate by MOCVD," *Semicond. Sci. Technol.*, vol. 34, no. 8, Aug. 2019, Art. no. 08LT01, doi: 10.1088/1361-6641/ab2c17.

- [43] J.-H. Park, R. McClintock, A. Jaud, A. Dehzangi, and M. Razeghi, "MOCVD grown β-Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field effect transistors on sapphire," *Appl. Phys. Exp.*, vol. 12, no. 9, Sep. 2019, Art. no. 095503, doi: 10.7567/1882-0786/ab3b2a.

- [44] Z. Hu et al., "The investigation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky diode with floating field ring termination and the interface states," *ECS J. Solid State Sci. Technol.*, vol. 9, no. 2, Jan. 2020, Art. no. 025001, doi: 10.1149/2162-8777/ab6162.

- [45] Z. Feng et al., "A 800 V β-Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor fieldeffect transistor with high-power figure of merit of over 86.3 MW cm<sup>-2</sup>," *Phys. Status Solidi (A)*, vol. 216, no. 20, Oct. 2019, Art. no. 1900421, doi: 10.1002/pssa.201900421.