## Integration of graphene oxide buffer layer/ graphene floating gate for wide memory window in Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au non-volatile (FLASH) applications

Cite as: Appl. Phys. Lett. **112**, 252102 (2018); https://doi.org/10.1063/1.5030020 Submitted: 18 March 2018 . Accepted: 02 June 2018 . Published Online: 18 June 2018

Mahesh Soni 回, Ajay Soni, and Satinder K. Sharma 回

## ARTICLES YOU MAY BE INTERESTED IN

Dual-gate MoS<sub>2</sub> transistors with sub-10nm top-gate high-k dielectrics Applied Physics Letters **112**, 253502 (2018); https://doi.org/10.1063/1.5027102

Negative differential resistance in GaN homojunction tunnel diodes and low voltage loss tunnel contacts

Applied Physics Letters 112, 252103 (2018); https://doi.org/10.1063/1.5035293

Investigation of multilayer WS<sub>2</sub> flakes as charge trapping stack layers in non-volatile memories

Applied Physics Letters 112, 231903 (2018); https://doi.org/10.1063/1.5024799

Appl. Phys. Lett. **112**, 252102 (2018); https://doi.org/10.1063/1.5030020 © 2018 Author(s).

## Integration of graphene oxide buffer layer/graphene floating gate for wide memory window in Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au non-volatile (FLASH) applications

Mahesh Soni,<sup>1</sup> Ajay Soni,<sup>2</sup> and Satinder K. Sharma<sup>1,a)</sup>

<sup>1</sup>School of Computing and Electrical Engineering (SCEE), Indian Institute of Technology (IIT) Mandi, Mandi, Himachal Pradesh 175005, India

<sup>2</sup>School of Basic Sciences (SBS), Indian Institute of Technology (IIT) Mandi, Mandi, Himachal Pradesh 175005, India

(Received 18 March 2018; accepted 2 June 2018; published online 18 June 2018)

The excellent electronic properties of graphene such as high density of states, work-function, and low dimensionality promote the usage of graphene as an efficient floating gate (FG) layer for downscaled, high density non-volatile flash memories (NVFMs). However, the chemical inertness of graphene requires a buffer layer for the uniform deposition of a high-k blocking layer (high-k blocking oxide/ buffer layer/graphene/SiO<sub>2</sub>/p-Si/Au). Herein, FG-NVFM devices are fabricated using few-layer graphene as a FG followed by deposition of spin-coated monolayer graphene oxide (GO) as a buffer layer. The simple, stress free deposition of GO decorated with the functional groups is anticipated for the uniform deposition of blocking oxide (Aluminum oxide, Al<sub>2</sub>O<sub>3</sub>) over GO/graphene/SiO<sub>2</sub>/p-Si/Au. Beyond this, it improves the interface (Al<sub>2</sub>O<sub>3</sub>/GO/graphene), leading to enhanced memory characteristics for the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM structure. The electrical characterizations of the fabricated FG-NVFM devices show a significantly wide memory window of ~4.3 V @  $\pm$ 7 V at 1 MHz and robust retention up to ~2 × 10<sup>13</sup> s (>15 years). These observations clearly reveal an efficient potential of graphene for FG and GO as a buffer layer for the future NVFM device applications. *Published by AIP Publishing*. https://doi.org/10.1063/1.5030020

Floating Gate non-volatile flash memory (FG-NVFM) is the most commonly used storage technology in the majority of consumer electronics.<sup>1–5</sup> In this regard, for high-density data storage, further downscaling of poly-silicon based FG is a challenge, owing to its inherent physical issues leading to ballistic transport of carriers, impact ionization in the blocking dielectric, and device reliability.<sup>2,5,6</sup> An important figure of merit for NVFM is large memory window ( $\delta W$ ) and long term data retention with low operating voltages.<sup>5</sup> As per the industry standards, for reliable memory functionality, a  $\delta W$  of  $\sim$ 1.5 V and data retention of  $\sim$ >10 years (before the NVFM losses  $\sim 50\%$  of the stored charge) are essential.<sup>5,7</sup> Therefore, to overcome the challenges faced with poly-silicon FG and to meet the benchmarks of NVFM, ultra-thin metal ( $\sim 1 \text{ nm}$ ) was demonstrated as an alternate FG in NVFM.<sup>8</sup> But the use of metal FG imposes its own fundamental issues like diffusion/ agglomeration into the dielectrics (tunnel and blocking), resulting in increased leakage current.<sup>1,2,6,9</sup>

Driven by this, graphene (monolayer thickness ~0.3 nm) has attracted attention of the scientific community, as an alternate scaled FG layer for NVFM applications.<sup>2,5–7,10</sup> The interest in graphene is owing to its intrinsic properties such as high density of states (DOS), high work function ( $\Phi_{graphene}$ ), and excellent thermal and chemical stability.<sup>2,5–7,10</sup> Specifically, for NVFM involving graphene as a FG, graphene sandwiched between the two dielectrics (tunnelling and blocking) forms a potential well owing to the high  $\Phi_{graphene}$ .<sup>5</sup> Hence, it results in the large  $\delta$ W and long-term data retention.<sup>2,5–7,10</sup> In fact,  $\Phi_{graphene}$  varies with the number of layers owing to its

interlayer screening, more pronounced for multilayer ( $\geq$ 3 layer) graphene, and tends to saturate beyond six layers.<sup>5,6,11–15</sup> Therefore, an accurate control over the number of graphene layers over a large area is desirable for electronic device applications and is a challenge.<sup>5,6</sup> Several reports on the graphene growth by mechanical and chemical exfoliation and epitaxial growth on SiC by chemical vapor deposition (CVD) are described in the past.<sup>16</sup> However, for electronic device applications, CVD has emerged as an imperative method for the large area defect-free graphene growth along with an efficient control over the number of layers.<sup>17</sup>

Furthermore, for nano-electronic device applications, the interface of graphene with the high-k blocking dielectric is extremely important.<sup>4,7</sup> The chemical inertness and nonavailability of dangling bonds on the graphene surface lead to interface reliability for high-k/graphene based nano-scaled devices.<sup>5,18</sup> However, few research groups have reported low-temperature atomic layer deposition (ALD) of dielectrics over graphene; unfortunately, the deposition leads to negative effects, such as generation of additional defect sites in the graphene, and degrades the device performance.<sup>18</sup> Therefore, in order to obtain a reliable interface between the dielectric and graphene, deposition of the metal/polymer buffer layer over graphene was reported in the past.<sup>18</sup> Hong et al.<sup>5</sup> demonstrated graphene-NVFM, utilizing an aluminum  $(\sim 1.1 \text{ nm})$  layer deposited over graphene and oxidized in air, to serve as a buffer layer for ALD of  $Al_2O_3$  (~35 nm). As already discussed and established, the metal layer leads to increased leakage current in the fabricated devices<sup>2,6,9</sup> and degrades the graphene electronic and intrinsic properties.<sup>18</sup> On the other hand, deposition of the polymeric buffer layer through the spin coating is found to be a cost effective and

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed: satinder@iitmandi. ac.in

efficient route and does not hamper the intrinsic properties of graphene FG.<sup>18</sup>

The present work demonstrates the stress-free deposition of the graphene oxide (GO) buffer layer (via spin-coating) over CVD grown few ( $\sim$ 3–4) layer graphene (GO/graphene/ SiO<sub>2</sub>/p-Si/Au). The intention for the use of the monolayer GO buffer layer is (i) utilization of functional groups for the pin hole free deposition of the blocking layer and (ii) low dimensionality and controlled deposition.<sup>7,19,20</sup> However, the few layer graphene with high  $\Phi_{graphene}$ , DOS, reduced conductivity in the c-axis, and low dimensionality favors its use as a FG in NVFM applications.<sup>2,5–7,10</sup> Additionally, ultrathin SiO<sub>2</sub> serves as a tunneling layer, while the high-k, Al<sub>2</sub>O<sub>3</sub> is used as a blocking layer in the present study.<sup>2,6</sup>

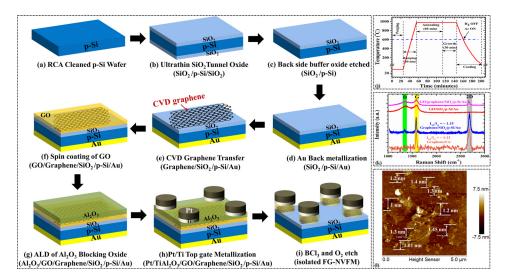

In order to investigate the electrical characteristics of few-layer CVD graphene FG based NVFM, a set of devices were fabricated as per the process flow shown in Figs. 1(a)–1(i). First, 2-in. p-Si wafers (1–10  $\Omega$  cm) with (100) orientation were cleaned using the standard RCA cleaning procedure [Fig. 1(a)]. Second, for ultrathin, high-quality SiO<sub>2</sub> tunnel oxide growth, the cleaned p-Si wafers were loaded to Rapid Thermal Oxidation (AS-One) at 25 °C under  $N_2$  flow (~800 sccm). Afterwards, the temperature was raised to 900 °C (ramp up  $\sim$ 25 °C/s), and for SiO<sub>2</sub> growth, an oxygen flow of ~800 sccm at 900 °C for 90 s was maintained. Finally, the temperature was ramped down from 900 °C to 25 °C at a rate of  $\sim$ 3 °C/s under a N<sub>2</sub> flow of  $\sim$ 800 sccm [Fig. 1(b)].<sup>7</sup> In the third step, the  $SiO_2/p-Si/SiO_2$  wafers were subjected to backside buffer oxide etch [Fig. 1(c)] and then the back metallization was performed (Au,  $\sim 100 \text{ nm}$ ) using an e-beam evaporator (TECHPORT) to result into SiO<sub>2</sub>/p-Si/Au [Fig. 1(d)] in the fourth step. For few-layer CVD graphene, cleaned Cu foils ( $\sim 25 \,\mu m$  thick) were loaded to the tube furnace at  $\sim 25 \,^{\circ}$ C and subsequently purged with Ar (~100 sccm) for 20 min. Thereafter, the temperature of the furnace was ramped up ( $\sim$ 30 °C/min) to  $\sim$ 980 °C under a H<sub>2</sub>:Ar flow of  $\sim$ 100:10 sccm at a pressure of  $\sim$ 7 mbar and annealed for next 60 min. For graphene growth, at  $\sim$ 980 °C, a mixture of CH<sub>4</sub>:H<sub>2</sub>:Ar 10:100:10 was injected into the furnace for 30 min at a pressure of  $\sim$ 8.5 mbar. As a next step, cooling was performed at a rate of  $\sim 20$  °C/min under a H<sub>2</sub> flow of  $\sim 100$  sccm up to  $\sim 600$  °C and an Ar flow of

$\sim 20$  sccm till  $\sim 40$  °C [Fig. 1(j)]. For the transfer of graphene sheets over SiO<sub>2</sub>/p-Si/Au, the PMMA (950 A1) thin film was spin-coated over graphene/Cu foils at 1000 rpm for 60 s and was kept on a hot plate at 100 °C for 5 min.<sup>21</sup> Here, PMMA protects the graphene layer and acts as a rigid support during the transfer process.<sup>22</sup> While, for Cu etching, the PMMA/ graphene/Cu structure was kept in ammonium persulphate solution (0.1 M) for  $\sim$ 4 h and was rinsed with DI water. After Cu etching, in the fifth step, the PMMA/graphene layer was gently scooped over the SiO2/p-Si/Au substrates, and thereafter, PMMA was removed using the acetone bath [Fig. 1(e)].<sup>22,23</sup> As discussed previously, the residues of metal over the transferred graphene degrade the device performance.<sup>2,5,6,9,24,25</sup> Conversely, the presence of undesirable PMMA residue over the transferred graphene may also increase the surface roughness and thereby degrade the interface, leading to non-uniform deposition of the blocking oxide and resulting in lower memory window, increased gate leakage current, and reduced reliability of the fabricated FG-NVFM.<sup>2,5,6,9,22,26–29</sup> Therefore,  $\mu$ -Raman spectroscopy measurements were performed to ensure the quality of the transferred few-layer graphene on SiO<sub>2</sub>/p-Si/Au substrates.<sup>5</sup> The  $\mu$ -Raman spectra show very low intensity "D" (~1350 cm<sup>-1</sup>) band peak "I<sub>D</sub>" as compared to the "G" ( $\sim 1580 \text{ cm}^{-1}$ ) band peak "I\_G" and result in  $I_D/I_G \sim 0.08$  and 0.1 for graphene/Cu and graphene/SiO<sub>2</sub>/p-Si/Au, whereas "2D" ( $\sim$ 2700 cm<sup>-1</sup>) band peak " $I_{2D}$ " with respect to the " $I_G$ " results in the  $I_{2D}/I_G$  $\sim 1.1$  [Fig. 1(k)] for both graphene/Cu and graphene/SiO<sub>2</sub>/p-Si/Au. These outcomes clearly demonstrate the presence of few (3-4) layers of graphene, and a very low intensity "D" band peak in Raman spectra signifies a defect free graphene growth and transfer, as reported in the past.<sup>5,30</sup> The defect free graphene used in the present work refers to the absence of undesirable defects and residues of metals or polymers over the transferred graphene.<sup>22,27-29,31</sup> After that, in the sixth step, the GO synthesized using the modified Hummers method,<sup>19</sup> at a concentration of 1 mg/ml in DI water, was spin-coated over the graphene/SiO<sub>2</sub>/p-Si/Au substrates at 1000 rpm for 2 min and dried at 50 °C for 5 min [Fig. 1(f)]. The  $\mu$ -Raman spectroscopy [Fig. 1(k)] was performed to confirm the presence of GO/graphene stack and GO over the desired substrates. Here, the Raman signature peaks of GO

FIG. 1. (a)–(i) Schematic process flow for the fabrication of CVD graphene based Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/ p-Si/Au FG-NVFM structure, (j) time line for the CVD graphene growth on Cu, (k) Raman Spectra for graphene/ Cu, graphene/SiO<sub>2</sub>/p-Si/Au, GO/SiO<sub>2</sub>/ p-Si/Au, and GO/graphene/SiO<sub>2</sub>/p-Si/ Au, and (I) AFM height profile analysis of GO sheets for a scan area of  $5 \times 5 \ \mu m^2$ .

and graphene are in line with the previous reports.<sup>16,21</sup> The tapping mode atomic force microscopy (AFM) measurement for a scan area of  $5 \times 5 \ \mu m^2$  [shown in Fig. 1(1)] clearly depicts that the GO sheets are distributed all over the sample surface, and the height profile analysis on the individual GO sheets confirms the thickness of  $\sim 1$  nm, consistent with the GO monolayer thickness reported in the literature.<sup>32,33</sup> To double check the thickness of GO used in the present work, an alternate imaging spectroscopic ellipsometry based mapping technique with variable wavelength  $(\lambda, 400-800 \text{ nm})$  using a Nanofilm EP4 (Accurion system) over a region of  $\sim 400 \times 400 \ \mu m^2$  was used.<sup>34–36</sup> Herein, for the calculation of optical constants and thickness mapping of GO sheets, a Cauchy model was used which confirmed the presence of monolayer ( $\sim 1 \text{ nm}$ ) GO and validated the AFM results.<sup>34–36</sup> Afterwards, as a seventh step,  $Al_2O_3$  was deposited over GO/graphene/SiO<sub>2</sub>/p-Si/Au using trimethylaluminum and water as precursors at  $\sim 200$  °C through ALD (BENEQ 300) [Fig. 1(g)]. For top gate electrode formation, Ti/Pt (10 nm/90 nm) was sputtered over the Al<sub>2</sub>O<sub>3</sub>/ GO/graphene/SiO<sub>2</sub>/p-Si/Au and patterned by standard lithography techniques [Fig. 1(h)]. The circular top gate electrode diameter was  $\sim 80 \,\mu m$ . To isolate each FG-NVFM device, the undesirable Al<sub>2</sub>O<sub>3</sub> and GO/graphene layers (present outside the device region) were removed using BCl<sub>3</sub> plasma  $\sim 15$  s and O<sub>2</sub> plasma  $\sim 2$  min, respectively [using Oxford Plasma Lab, Fig. 1(i)]. In addition, from each of the aforesaid device fabrication steps, reference samples were held in reserve for further electrical, chemical, and physical characterizations, optimization of various parameters, and fabrication of control samples. The thickness of the ultrathin SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> films (measured using a J. A. Woolman Imaging Ellipsometer) was found to be  $\sim 5 \pm 0.1$  nm and  $\sim 15 \pm 0.2$  nm, respectively. Electrical characterization and charge storage capability of the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM structures and control samples (Pt/Ti/Al2O3/GO/SiO2/p-Si/ Au, Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/graphene/ SiO<sub>2</sub>/p-Si/Au, Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/p-Si/Au, and Pt/Ti/SiO<sub>2</sub>/p-Si/Au) were systematically characterized by Capacitance-Gate Voltage (C-V), Gate leakage current density-Gate Voltage (|J|-V), and Capacitance-Time (C-T) measurements using a Keithley 4200 SCS attached to a cascade probe station.

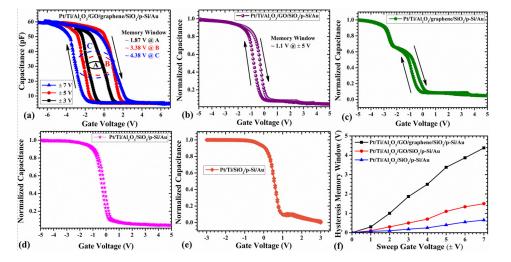

Figure 2 shows the cyclic C-V measurements for the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM devices and their control samples as a function of different sweep voltages:  $\pm 3 \text{ V}$ ,  $\pm 5 \text{ V}$ , and  $\pm 7 \text{ V}$  at 1 MHz. While performing the cyclic C-V measurements, the gate voltage swept from inversion  $(V_{g+})$  to accumulation  $(V_{g-})$ (forward sweep) and accumulation  $(V_{g-})$  to inversion  $(V_{g+})$ (reverse sweep). As depicted from the C-V curves, compared to control samples, the Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/ Au shows a significant flat band shift between forward and reverse sweeps, also termed as  $\delta W$ . The observed  $\delta W$  for the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM [Fig. 2(a)] is around 1.87 V @  $\pm 3$  V (marked as "A"), 3.38 V @  $\pm$ 5 V (marked as "B"), and 4.38 V @  $\pm$ 7 V (marked as "C"). Also, the cyclic C-V measurements show remarkable characteristics favourable for memory devices such as (i) clockwise hysteresis centred  $\sim 0$  V, indicating the low voltage operation of the fabricated NVFM with considerable high/low capacitance states and (ii) fast switching of capacitance during forward and reverse sweeps. The obtained large  $\delta W$  under low sweep voltages is sufficient for reliable data storage, thus confirming the ability of few-layer graphene as a potential FG layer in NVFM.

Furthermore, an additional hump at the mid depletion in the cyclic C-V for Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/graphene/SiO<sub>2</sub>/Si/Au [Fig. 2(c)] during forward and reverse sweeps is noticed. Whereas, for Pt/Ti/Al2O3/GO/graphene/SiO2/p-Si/Au FG-NVFM as shown in Fig. 2(a), this hump in the mid depletion region vanishes. It clearly perceived that there is an existence of electrically active traps at the interface of Al<sub>2</sub>O<sub>3</sub>/graphene and responded at -2 to -3 V for the Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/graphene/ SiO<sub>2</sub>/p-Si/Au structure. However, once these electrically active traps at the Al<sub>2</sub>O<sub>3</sub>/graphene interface are filled, due to fermi level pinning they become electrically inactive, which is evidently revealed from C-V characteristics of the Pt/Ti/  $Al_2O_3$ /graphene/SiO<sub>2</sub>/p-Si/Au structure [Fig. 2(c)] from -3to -5 V gate voltage sweep. Therefore, to enhance the reliability and long term retention of fabricated FG-NVFM, in the present work, an additional mono-layer of GO is deposited between Al<sub>2</sub>O<sub>3</sub> and graphene, which facilitates the high quality and uniform deposition of Al<sub>2</sub>O<sub>3</sub> for the Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/ GO/graphene/SiO<sub>2</sub>/p-Si/Au structure with an improved interface as clearly depicted in Fig. 2(a).

FIG. 2. Cyclic Capacitance-Gate Voltage measurements at 1 MHz for (a) Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM under different sweep voltages; Control Samples (b) Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/SiO<sub>2</sub>/p-Si/Au, (c) Pt/ Ti/Al<sub>2</sub>O<sub>3</sub>/GO/SiO<sub>2</sub>/p-Si/Au, (d) Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/p-Si/Au, (e) Pt/Ti/ SiO<sub>2</sub>/p-Si/Au, and (f) Summary of the obtained memory window with respect to various fabricated device structures.

Table I summarizes and presents a comparison of the present work with the previously reported NVFM with CNT, graphene, GO, rGO, and NrGO as FG layers. Additionally, the total number of charge carriers stored per unit area ( $N_{graphene}$ ) in the FG can be calculated from the following relation:<sup>1,2,5,6,10</sup>

$$N_{graphene} = \frac{\delta \mathbf{W} \times \mathbf{C}_{\mathrm{Al}_2 \mathrm{O}_3}}{q},\tag{1}$$

where  $C_{Al_2O_3} = \frac{\epsilon_0 \times \epsilon_{Al_2O_3}}{t_{Al_2O_3}}$ , with  $\epsilon_0$  being the permittivity of the free space, and  $\epsilon_{Al_2O_3}$  and  $t_{Al_2O_3}$  the relative permittivity and measured thickness of ALD Al<sub>2</sub>O<sub>3</sub>, respectively, along with q being the electronic charge. Therefore, based on Eq. (1), the computed N<sub>graphene</sub> at  $\pm 7$  V is  $\sim 2 \times 10^{13}$  cm<sup>-2</sup> and is found comparable to the reported DOS for few-layer graphene ( $\sim 4.4 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>).<sup>1,2,5,6</sup>

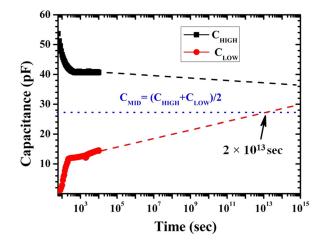

For the real world applications, the retention (C-T) characteristics of the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/ p-Si/Au FG-NVFM were investigated. The retention in NVFM refers to the potential lifetime of the data stored without electrical refreshing. As shown in Fig. 3, the C-T analysis of the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM with a write pulse of  $\pm$ 7 V was applied for 0.1 s with a read voltage of ~-1 V, which is close to the flat band voltage.<sup>7</sup> Based on the voltage of the write applied pulse, the C-T characteristics result in high (C<sub>HIGH</sub> @ -7 V) and low (C<sub>LOW</sub> @ +7 V) capacitance states, while the average (50%) of the two capacitance states is the mid capacitance C<sub>MID</sub> = (C<sub>HIGH</sub> + C<sub>LOW</sub>)/2. The C-T characteristics for the fabricated FG-NVFM can be divided into two regions. In the first region for ~10<sup>2</sup> s, where an exponential decay in C<sub>HIGH</sub> and

TABLE I. Comparison and Summary of the FG-NVFM.

| FLASH memory structure                                                                                                 | $\delta W$ (~in V) @<br>gate voltage (in V) | Retention<br>(in s)        | References |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------|------------|

| TaN/Al <sub>2</sub> O <sub>3</sub> (~22 nm)/Multi-layer                                                                | 3@±14                                       |                            | 2          |

| rGO ( $\sim$ 1.5 nm)/SiO <sub>2</sub> ( $\sim$ 8 nm)/                                                                  | 5.8 @ ±16                                   |                            |            |

| p-Si                                                                                                                   | 8@±18                                       |                            |            |

|                                                                                                                        | 9.4 @ ±20                                   |                            |            |

| Au/Al/Ti/Al <sub>2</sub> O <sub>3</sub> ( $\sim$ 35 nm)/graphene ( $\sim$ 0.3 nm)/SiO <sub>2</sub> ( $\sim$ 5 nm)/p-Si | 2@±7                                        | $\sim 10^{8}$              | 5          |

| Au/Al/Ti/Al <sub>2</sub> O <sub>3</sub> ( $\sim$ 35 nm)/graphene ( $\sim$ 1.5 nm)/SiO <sub>2</sub> ( $\sim$ 8 nm)/p-Si | 6@±7                                        |                            |            |

| Al/PMMA (~50 nm)/NrGO                                                                                                  | 1.8@±3                                      | $\sim 10^5$                | 7          |

| $(\sim 1.5 \text{ nm})/\text{SiO}_2 (\sim 5 \text{ nm})/\text{p-Si}$                                                   | 2@+3 to $-5$                                |                            |            |

|                                                                                                                        | 3.3@±7                                      |                            |            |

| TaN/Al2O3 (~15 nm)/Multi-layer                                                                                         | 1.5@±8                                      |                            | 6          |

| rGO (~1.5 nm)/SiO <sub>2</sub> (~8 nm)/                                                                                | 2.6@±10                                     |                            |            |

| p-Si                                                                                                                   | 4.2@±14                                     |                            |            |

|                                                                                                                        | 6.8 @ ±18                                   |                            |            |

| TaN/Al <sub>2</sub> O <sub>3</sub> (~15 nm)/GO                                                                         | 2.3 @ 5 to 8                                |                            | 32         |

| $(\sim 1 \text{ nm})/\text{SiO}_2 (\sim 5 \text{ nm})/\text{p-Si}$                                                     | 7.5 @ −5 to 14                              |                            |            |

| $\begin{array}{l} TaN/Al_2O_3~(\sim\!15~nm)/rGO/SiO_2 \\ (\sim\!8~nm)/p\text{-}Si \end{array}$                         | 1.4 @ ±4                                    |                            |            |

| Pt/HfAlO/CNT/HfAlO/p-Si                                                                                                | 0.4 @ ±3                                    | $\sim 10^4$                | 37         |

| Pt/Ti/Al <sub>2</sub> O <sub>3</sub> (~15 nm)/GO                                                                       | 1.87@±3                                     | $\sim \! 2 \times 10^{13}$ | This work  |

| $(\sim 1 \text{ nm})/\text{graphene} (\sim 1.5 \text{ nm})/$                                                           | 3.38 @ ±5                                   |                            |            |

| SiO <sub>2</sub> (~5 nm)/p-Si/Au                                                                                       | 4.38 @ ±7                                   |                            |            |

FIG. 3. Data Retention (C-T) characteristics for the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/ GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM.

exponential rise for  $C_{LOW}$  are noticed, attributing to narrowing  $\delta W$ . In the second region, beyond  $\sim 10^3$  s, the  $C_{HIGH}$  and  $C_{LOW}$  states saturate and seem parallel to each other, dictating excellent long-term charge retention characteristics. On further extrapolation of the C-T characteristics (>10<sup>4</sup> s), the  $C_{HIGH}$  and  $C_{LOW}$  remain distinguishable for  $\sim 10^{13}$  s, ahead of time the  $C_{LOW}$  coincides with  $C_{MID}$  at  $\sim 2 \times 10^{13}$  s. Hence, the retention of the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/ SiO<sub>2</sub>/p-Si/Au FG-NVFM is approximately >15 years. The observed retention in the fabricated FG-NVFM is considerably higher than the reported retention value in the literature for CNT, GO, rGO, and NrGO-based FG-NVFM.<sup>2,5-7,32,37</sup> Therefore, the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM structure is suitable for next generation NVFM applications operating at low voltages.

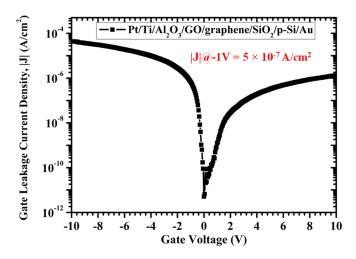

The gate leakage current density (|J|) as a function of gate voltage (V) characteristic for the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM structure is shown in Fig. 4. The measured |J| of ~4 × 10<sup>-5</sup> A/cm<sup>2</sup> @ -10 V for the fabricated NVFM structure is comparable with the reported literature.<sup>5</sup> On the other hand, the significantly higher  $\delta W$  (~4.38 V) and minimal leakage current density (~5 × 10<sup>-7</sup> A/cm<sup>2</sup> @ -1 V) are indications of the

FIG. 4. Leakage Current Density-Gate Voltage (|J|-V) plot for the fabricated Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au FG-NVFM structure.

enhanced reliability and feasibility for the use of the Pt/Ti/ Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au structure for NG-NVFM applications.<sup>5</sup>

In summary, the considerably wide memory window and long term data retention for the fabricated  $Pt/Ti/Al_2O_3/$ GO/graphene/SiO<sub>2</sub>/p-Si/Au suggest the potential of graphene and GO as a FG and buffer layer for NVFM applications. The low dimensionality, high work function, and high density of states support the use of graphene as FG, while the GO buffer layer over graphene favors the uniform and pin hole free deposition of blocking layer (Al<sub>2</sub>O<sub>3</sub>). The benefits of the fabricated FG-NVFM are as follows: first, it can be utilized for fabrication of low-cost memories, and second, the compatibility of the adopted approach with the existing semiconductor processing, thus paving the way for future electronic applications.

The authors thank the C4DFED and AMRC, IIT Mandi, for the graphene growth and electrical and material characterization facilities. The authors are also thankful to CeNSE, IISC Bangalore, (under INUP) for the deposition of tunnel and blocking layers and etching facilities for the fabrication of device structures. M.S. also thanks IIT Mandi for the financial support.

- <sup>1</sup>S. Jang, E. Hwang, J. H. Lee, H. S. Park, and J. H. Cho, Small **11**(3), 311–318 (2014).

- <sup>2</sup>A. Mishra, A. Janardanan, M. Khare, H. Kalita, and A. Kottantharayil, IEEE Electron Device Lett. **34**(9), 1136–1138 (2013).

- <sup>3</sup>A. Di Bartolomeo, H. Rücker, P. Schley, A. Fox, S. Lischke, and K.-Y. Na, Solid-State Electron. **53**(6), 644–648 (2009).

- <sup>4</sup>R. Yang, C. Zhu, J. Meng, Z. Huo, M. Cheng, D. Liu, W. Yang, D. Shi, M. Liu, and G. Zhang, Sci. Rep. 3, 2126 (2013).

- <sup>5</sup>A. J. Hong, E. B. Song, H. S. Yu, M. J. Allen, J. Kim, J. D. Fowler, J. K. Wassei, Y. Park, Y. Wang, and J. Zou, ACS Nano **5**(10), 7812–7817 (2011).

- <sup>6</sup>A. Mishra, H. Kalita, M. Waikar, A. Gour, M. Bhaisare, M. Khare, M. Aslam, and A. Kottantharayil, in 2012 4th IEEE International Memory Workshop (IMW) (IEEE, 2012), pp. 1–4.

- <sup>7</sup>M. Soni, A. Soni, and S. K. Sharma, Org. Electron. **51**, 48–53 (2017).

- <sup>8</sup>S. Jayanti, X. Yang, R. Suri, and V. Misra, in 2010 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2010), pp. 5.3.1–5.3.4.

- <sup>9</sup>S. Jayanti, Y. Xiangyu, and V. Misra, in 2011 3rd IEEE International Memory Workshop (IMW) (2011), pp. 1–4.

- <sup>10</sup>S. Bertolazzi, D. Krasnozhon, and A. Kis, ACS Nano 7(4), 3246–3252 (2013).

- <sup>11</sup>D. Ziegler, P. Gava, J. Güttinger, F. Molitor, L. Wirtz, M. Lazzeri, A. Saitta, A. Stemmer, F. Mauri, and C. Stampfer, Phys. Rev. B 83(23), 235434 (2011).

- <sup>12</sup>N. J. Lee, J. W. Yoo, Y. J. Choi, C. J. Kang, D. Y. Jeon, D. C. Kim, S. Seo, and H. J. Chung, Appl. Phys. Lett. **95**(22), 222107 (2009).

- <sup>13</sup>A. Misra, M. Waikar, A. Gour, H. Kalita, M. Khare, M. Aslam, and A. Kottantharayil, Appl. Phys. Lett. **100**(23), 233506 (2012).

- <sup>14</sup>H. Hibino, H. Kageshima, M. Kotsugi, F. Maeda, F. Z. Guo, and Y. Watanabe, Phys. Rev. B **79**(12), 125437 (2009).

- <sup>15</sup>J. T. Robinson, J. Culbertson, M. Berg, and T. Ohta, Sci. Rep. 8(1), 2006 (2018).

- <sup>16</sup>M. Soni, P. Kumar, J. Pandey, S. K. Sharma, and A. Soni, Carbon 128, 172–178 (2018).

- <sup>17</sup>R. Muñoz and C. Gómez-Aleixandre, Chem. Vapor Deposition **19**(10-11-12), 297–322 (2013).

- <sup>18</sup>H. Alles, J. Aarik, J. Kozlova, A. Niilisk, R. Rammula, and V. Sammelselg, *Graphene–Synthesis, Characterization, Properties and Applications*, edited by J. R. Gong (InTech, 2011), pp. 99–114.

- <sup>19</sup>M. Soni, T. Arora, R. Khosla, P. Kumar, A. Soni, and S. K. Sharma, IEEE Sens. J. 16(6), 1524–1531 (2016).

- <sup>20</sup>G. Eda, A. Nathan, P. Wöbkenberg, F. Colleaux, K. Ghaffarzadeh, T. D. Anthopoulos, and M. Chhowalla, Appl. Phys. Lett. **102**(13), 133108 (2013).

- <sup>21</sup>G. Deokar, J. Avila, I. Razado-Colambo, J.-L. Codron, C. Boyaval, E. Galopin, M.-C. Asensio, and D. Vignaud, Carbon **89**, 82–92 (2015).

- <sup>22</sup>X. Liang, B. A. Sperling, I. Calizo, G. Cheng, C. A. Hacker, Q. Zhang, Y. Obeng, K. Yan, H. Peng, and Q. Li, ACS Nano 5(11), 9144–9153 (2011).

- <sup>23</sup>C. Mattevi, H. Kim, and M. Chhowalla, J. Mater. Chem. 21(10), 3324–3334 (2011).

- <sup>24</sup>A. Misra, S. Sadana, S. Suresh, M. Bhaisare, S. Srinivasan, M. Waikar, A. Gaur, and A. Kottantharayil, MRS Proc. **1288**, mrsf10-1288-g11-48 (2011).

- <sup>25</sup>P. Blomme, A. Cacciato, D. Wellekens, L. Breuil, M. Rosmeulen, G. Kar, S. Locorotondo, C. Vrancken, O. Richard, and I. Debusschere, IEEE Electron Device Lett. 33(3), 333–335 (2012).

- <sup>26</sup>X. Tang, N. Reckinger, O. Poncelet, P. Louette, F. Ureña, H. Idrissi, S. Turner, D. Cabosart, J.-F. Colomer, and J.-P. Raskin, Sci. Rep. 5, 13523 (2015).

- <sup>27</sup>Y. C. Lin, C. C. Lu, C. H. Yeh, C. Jin, K. Suenaga, and P. W. Chiu, Nano Lett. **12**(1), 414–419 (2012).

- <sup>28</sup>Y. Chen, X. L. Gong, and J. G. Gai, Adv. Sci. 3(8), 1500343 (2016).

- <sup>29</sup>H. C. Lee, W.-W. Liu, S.-P. Chai, A. R. Mohamed, A. Aziz, C.-S. Khe, N. M. Hidayah, and U. Hashim, RSC Adv. 7(26), 15644–15693 (2017).

- <sup>30</sup>Y. Liu, Z. Liu, W. S. Lew, and Q. J. Wang, Nanoscale Res. Lett. **8**(1), 335 (2013).

- <sup>31</sup>P. T. Araujo, M. Terrones, and M. S. Dresselhaus, Mater. Today 15(3), 98–109 (2012).

- <sup>32</sup>S. Wang, J. Pu, D. S. Chan, B. J. Cho, and K. P. Loh, Appl. Phys. Lett. 96(14), 143109 (2010).

- <sup>33</sup>S. Stankovich, D. A. Dikin, G. H. Dommett, K. M. Kohlhaas, E. J. Zimney, E. A. Stach, R. D. Piner, S. T. Nguyen, and R. S. Ruoff, Nature 442(7100), 282 (2006).

- <sup>34</sup>S. Funke, U. Wurstbauer, B. Miller, A. Matković, A. Green, A. Diebold, C. Röling, and P. Thiesen, Appl. Surf. Sci. 421, 435–439 (2017).

- <sup>35</sup>I. Jung, M. Vaupel, M. Pelton, R. Piner, D. A. Dikin, S. Stankovich, J. An, and R. S. Ruoff, J. Phys. Chem. C 112(23), 8499–8506 (2008).

- <sup>36</sup>U. Wurstbauer, C. Röling, U. Wurstbauer, W. Wegscheider, M. Vaupel, P. H. Thiesen, and D. Weiss, Appl. Phys. Lett. **97**(23), 231901 (2010).

- <sup>37</sup>X. B. Lu and J. Y. Dai, Appl. Phys. Lett. **88**(11), 113104 (2006).