#### Hardware-Efficient & High-Throughput VLSI-Architectures of Convolutional-Neural-Network Accelerator for Edge Applications

Thesis submitted in partial fulfillment of the requirements for the degree of

#### **DOCTOR OF PHILOSOPHY**

by

Md. Najrul Islam

Enrollment No. D18064

Supervisors

Dr. Rahul Shrestha (Guide)

&

Prof. Shubhajit Roy Chowdhury(Co-Guide)

SCHOOL OF COMPUTING AND ELECTRICAL ENGINEERING

INDIAN INSTITUTE OF TECHNOLOGY MANDI

Oct. 2025

| In the name of the Almighty, whose mercy surrounds all endeavors.            |

|------------------------------------------------------------------------------|

| I dedicate this work to my family, whose love and sacrifices shaped my path. |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

**Declaration by the Research Scholar**

I hereby declare that the entire work embodied in this thesis entitled "Hardware-Efficient

& High-Throughput VLSI-Architectures of Convolutional-Neural-Network Accelera-

tor for Edge Applications" is the result of investigations carried out by me in the School

of Computing and Electrical Engineering, Indian Institute of Technology Mandi, Mandi,

Himachal Pradesh, India, under the supervision of Dr. Rahul Shrestha (Guide), Associate

Professor, School of Computing and Electrical Engineering, Indian Institute of Technol-

ogy Mandi, Mandi, Himachal Pradesh, India, and Prof. Shubhajit Roy Chowdhury (Co-

Guide), Professor, School of Computing and Electrical Engineering, Indian Institute of

Technology Mandi, Mandi, Himachal Pradesh, India

I also declare that it has not been submitted elsewhere for the award of any degree or

diploma. In keeping with general practice, due acknowledgments have been made wherever

the work described is based on the findings of other investigators. Any omissions that might

have occurred due to oversight or error in judgement are regretted.

Md. Najrul Islam

Date: oth Oct. 2025

Place: IIT Mandi,

Himachal Pradesh, India

Enrollment No. D18064

School of Computing and Electrical Engineering,

Indian Institute of Technology Mandi,

Mandi, Himachal Pradesh, India - 175075.

#### **Declaration by the Research Advisors**

It is certified that the entire work in this thesis entitled "Hardware-Efficient & High-Throughput VLSI-Architectures of Convolutional-Neural-Network Accelerator for Edge Applications" has been carried out by Md. Najrul Islam, Enrollment No. D18064, under our supervision and guidance for the degree of Doctor of Philosophy in the School of Computing and Electrical Engineering, Indian Institute of Technology Mandi, Mandi, Himachal Pradesh, India.

To the best of our knowledge and belief, present thesis completed by **Md. Najrul Islam** fulfils the requirements of the Ph.D. ordinance of the Indian Institute of Technology Mandi, Mandi, Himachal Pradesh, India. It contains original work of the candidate and no part of it has been submitted elsewhere for any degree or diploma.

Dr. Rahul Shrestha (Guide)

**Associate Professor**

School of Computing and Electrical

Engineering,

Indian Institute of Technology Mandi,

Mandi, Himachal Pradesh, India - 175075.

Prof. Shubhajit Roy Chowdhury

(Co-Guide)

Professor, School of Computing and

Electrical Engineering,

Indian Institute of Technology Mandi,

Mandi, Himachal Pradesh, India - 175075.

## **Acknowledgments**

I bow to the *Almighty*, source of all knowledge and strength, without whose will nothing is possible. First and foremost, I would like to express my deepest and most sincere gratitude to my guide, Dr. Rahul Shrestha. His unwavering support, belief in my potential, and constant encouragement have played an instrumental role in shaping this research. He stood by me during challenging times, offering not only academic guidance but also personal support and reassurance. His patience, clarity of thought, and tireless efforts have inspired me throughout this journey. I consider myself extremely fortunate to have had him as my mentor, and this work would not have been possible without his constant presence and belief in me.

I would also like to sincerely thank my co-guide, Prof. Shubhajit Roy Chowdhury, for his support and presence throughout this research. His insights, feedback, and encouragement during various stages of the work have been valuable, and I am grateful for the time and consideration he offered during this journey.

I would like to express my heartfelt gratitude.....

To Dr. Hitesh Shrimali, for his constant encouragement, support and inspiration throughout the thesis journey. I am thankful to him for sharing his immense knowledge about VLSI design and valuable feedback towards my thesis work.

To Prof. Anup Dandapat for his invaluable guidance and encouragement at a crucial stage of my academic journey. It was his suggestion and support that inspired me to pursue a Ph.D. at IIT, a decision that has profoundly shaped my professional and personal growth.

To Dr. Ranjeet Jha and Dhaval Patel for their invaluable support in helping me understand the Python implementation of AI concepts. Dr. Jha's guidance in resolving my doubts and Dhaval Patel's detailed hands-on explanation videos both played a significant role in

strengthening the software implementation part of my work.

To Dr. Vipin Kizheppatt, whose insightful YouTube videos helped me clear many doubts and overcome hurdles related to hardware-software co-design.

To Dr. Sandeep Kumar Mishra for his guidance and support in helping me learn and navigate Electronic Design Automation (EDA) tools. His expertise and patient instruction provided a strong foundation for the technical aspects of my research.

To Dr. Rohit Chaurasiya for his selfless support, patience, and loving-kindness throughout my Ph.D. journey. He taught me the ASIC design flow, helped me understand numerous tools, and cleared countless doubts along the way. Our technical discussions not only deepened my knowledge but also made the learning process enjoyable. I truly cherish the valuable time spent together and the beautiful memories we created during this journey.

To Dr. Anuj Verma for his helpful guidance in clarifying my doubts related to inferring BRAM and managing clocks in FPGA design.

To Dr. Sushantha Gogoi for encouraging me to join IIT Mandi and for his insightful suggestion to explore hardware-software co-design in response to a specific challenge I was facing.

To the anonymous reviewers of IEEE TCAS-I, TVLSI, ISVLSI and VLSID, for their critical assessments towards the work carried out in my thesis.

To Shakti, Rahul Sharma, Nandit, Saurabh, Puneet Mishra, and Dr. Dinesh for technical and entertaining discussions.

To Sahil, Ayush, and Alip for their selfless help.

To all of my labmates for the joyful memories, shared laughter, and the sense of community that made the work environment both inspiring and enjoyable.

To Tarun Verma from Digital Analog Electronics Lab, Shivam Prajapati from Control System Laboratory and Sumit Maan from Signal Processing and Communication Lab for their kind cooperation.

To Nalini Ma'am, Rakhi Ma'am, Monu sir, Shiv, and all other staff from SCEE office and academic section, finance Section and library section for their kind-coperation and patience throughout the thesis journey.

To Ravi, Chaman Lal ji, and Narnder ji, caretaker of Dashir and BeasKund hostels, for

their cooperation in listening and addressing my concerns.

To Ashish Tiwari, Kanchan Singh Rana, Saurabh Dhiman, Shashwat, Shakti, Prashant, Monu, Shubham, and Aisharya for all the fruitful discussions during the course work and for their time in creating unforgettable memories.

To all staff of health centre, IIT Mandi, for their immense help during tough times.

To my mother, sister, brother, and wife for their unwavering love, support, and encouragement throughout this journey.

To all the sentient beings who knowingly or unknowingly have added value to my thesis work.

Md. Najrul Islam

#### **Abstract**

Rapid advancement of artificial intelligence (AI) and deep learning has driven the need for efficient hardware accelerators that are capable of handling complex convolutional neural network (CNN) computations. Though conventional processors like CPUs and GPUs are widely used, they are not ideally suited for the deployment of edge applications due to limitations in energy efficiency, data movement, and processing throughput. In this doctoral thesis, these challenges are addressed by presenting custom very-large scale-integration (VLSI) architectures tailored for CNN acceleration, optimized for both inference and training in resource-constrained environments. The proposed adaptive convolution mapping technique achieves a 1.71× improvement in the computation per multiply-accumulate (MAC) unit over the state-of-the-art designs. In addition, an uninterrupted processing strategy, leveraging a random-access line-buffer (RALB), delivers 2.55× higher throughput by eliminating memory stalls and maintaining a continuous dataflow. On further optimizing the energy efficiency, the suggested designs emphasize extensive local data reuse across all the CNN layers, leading to a 3.4× improvement in energy efficiency over state-of-the-art works. Furthermore, an unified CNN-accelerator design is presented in this thesis that supports both training and inference on a single architectural platform. It is incorporated with the optimized forward and backward passes, efficient data reuse, and scalable kernel mapping strategies to support a broad range of CNN workloads. Therefore, such unified CNN accelerator achieves 1.36× higher energy efficiency compared to reported training accelerators. The hardware architectures are implemented and evaluated on field-programmable gate-array (FPGA) platforms, confirming their ability to deliver high throughput, low power consumption, and scalability across a variety of CNN models.

**Keywords**: CNN Accelerator, Deep Learning Hardware, FPGA Implementation, Energy-Efficient AI, Convolution Mapping, Data Reuse, VLSI Architecture, Inference and Training, Edge AI, Memory Optimization, Low-Power Computing, AI Hardware, Hardware Acceleration, Real-Time AI Processing.

# **Contents**

| A١ | bstrac  | et            |              |                                                       | j    |

|----|---------|---------------|--------------|-------------------------------------------------------|------|

| Li | st of I | Figures       |              |                                                       | ix   |

| Li | st of T | <b>Fables</b> |              |                                                       | xiv  |

| Sy | mbol    | S             |              |                                                       | xxii |

| 1  | Intr    | oductio       | n            |                                                       | 1    |

|    | 1.1     | Artific       | ial Intellig | ence                                                  | 1    |

|    | 1.2     | Applic        | ations and   | Impact of AI                                          | 2    |

|    | 1.3     | Key C         | omponents    | s of AI                                               | 5    |

|    | 1.4     | Motiva        | ation for C  | NN-Centric Hardware Acceleration                      | 6    |

|    | 1.5     | Convo         | lutional No  | eural Networks: From Intuition to Implementation      | 8    |

|    |         | 1.5.1         | Human's      | Object Identification versus CNN Working Mechanism:   |      |

|    |         |               | An Analo     | ogy                                                   | 8    |

|    |         | 1.5.2         | Understa     | nding CNNs: A Hierarchical Approach to Image Recogni- |      |

|    |         |               | tion         |                                                       | 9    |

|    |         |               | 1.5.2.1      | Feature Extraction: Convolutional Layers              | 10   |

|    |         |               | 1.5.2.2      | Non-Linearity: Activation Function                    | 10   |

|    |         |               | 1.5.2.3      | Dimensionality Reduction: Pooling Layers              | 11   |

|    |         |               | 1.5.2.4      | Higher-Level Feature Representation                   | 11   |

|    |         |               | 1.5.2.5      | Classification: Fully Connected Layers and Output     | 12   |

|    | 1.6     | Accura        | acv and Co   | omplexity Trade-offs in AI Models                     | 13   |

|   | 1.7  | CNN I   | Hardware Accelerators: Addressing Computational Challenges in AI | 15 |

|---|------|---------|------------------------------------------------------------------|----|

|   | 1.8  | Literat | cure Review and Research Gaps                                    | 17 |

|   |      | 1.8.1   | Early Developments in CNN Acceleration                           | 17 |

|   |      | 1.8.2   | Adaptive Kernel Mapping                                          | 17 |

|   |      | 1.8.3   | Uninterrupted Processing and Dataflow Techniques                 | 18 |

|   |      | 1.8.4   | Full-Model Data Reuse                                            | 18 |

|   |      | 1.8.5   | Training Accelerators                                            | 19 |

|   |      | 1.8.6   | Research Gaps                                                    | 19 |

|   | 1.9  | Contri  | butions of the Thesis                                            | 20 |

| 2 | Har  | dware-l | Efficient CNN Accelerator with Adaptive Convolution Mapping      | 23 |

|   | 2.1  | Introdu | uction                                                           | 23 |

|   | 2.2  | Hardw   | vare Inefficiency in Conventional CNN Accelerators               | 25 |

|   | 2.3  | Propos  | sed Architectures                                                | 28 |

|   |      | 2.3.1   | High-Level Architecture of Hardware Accelerator                  | 28 |

|   |      | 2.3.2   | Proposed I-Buffer Architecture                                   | 30 |

|   |      |         | 2.3.2.1 Micro-architecture of Line Buffer                        | 32 |

|   |      | 2.3.3   | Suggested VLSI-Architectures for Filter Buffer and PMAU          | 33 |

|   | 2.4  | Experi  | mental Results & Comparison                                      | 35 |

|   | 2.5  | Summ    | ary                                                              | 37 |

| 3 | Desi | gn of H | High-Throughput and Energy-Efficient CNN Accelerator: Tech-      |    |

|   | niqu | ies and | Architectures                                                    | 39 |

|   | 3.1  | Introdu | uction                                                           | 39 |

|   | 3.2  | Prereq  | uisite and Research Challanges                                   | 42 |

|   |      | 3.2.1   | System Model                                                     | 42 |

|   |      | 3.2.2   | Research Challenges                                              | 44 |

|   |      |         | 3.2.2.1 Energy-Efficient Data Flow                               | 44 |

|   |      |         | 3.2.2.2 Throughput Reduction due to Interruption                 | 45 |

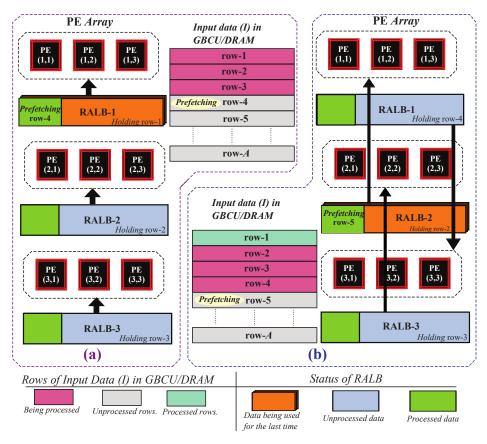

|   | 3.3  | Propos  | sed Technique and Architecture                                   | 46 |

|   |      | 3.3.1   | Uninterrupted-Processing Technique                               | 46 |

|   |                      | 3.3.2                                              | Proposed Hardware Architectures          |                                   | 48                                                                                                         |

|---|----------------------|----------------------------------------------------|------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------|

|   |                      |                                                    | 3.3.2.1 Low-Latency CNN-Accelerator      | Architecture                      | 48                                                                                                         |

|   |                      |                                                    | 3.3.2.2 Technique for Efficient Data Re  | euse and High-Throughput          |                                                                                                            |

|   |                      |                                                    | Computation                              |                                   | 50                                                                                                         |

|   | 3.4                  | Imple                                              | nentation Results, Comparisons and Hardw | are Validation                    | 52                                                                                                         |

|   |                      | 3.4.1                                              | FPGA Implementation Results              |                                   | 52                                                                                                         |

|   |                      | 3.4.2                                              | Comparison with the State-of-the-Art Imp | plementations                     | 55                                                                                                         |

|   |                      | 3.4.3                                              | Peak Throughput Issues due to DRAM Ba    | andwidth Limitation               | 58                                                                                                         |

|   |                      | 3.4.4                                              | Compatibility with State-of-the-Art CNN  | Models                            | 59                                                                                                         |

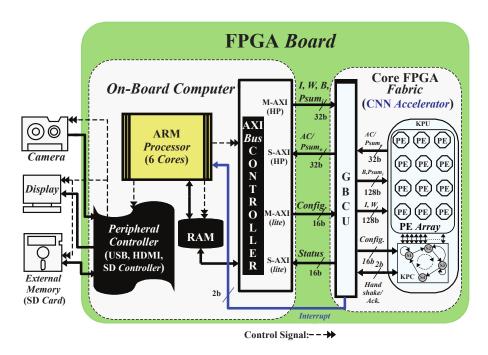

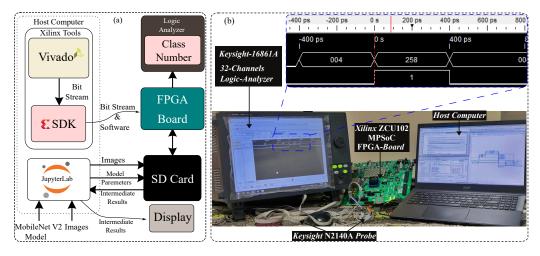

|   |                      | 3.4.5                                              | Hardware Validation of the Proposed CNI  | N Accelerator                     | 59                                                                                                         |

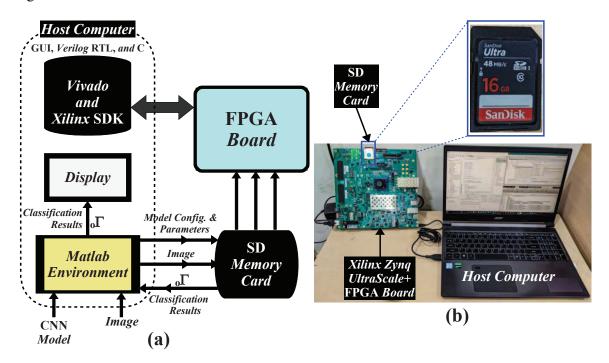

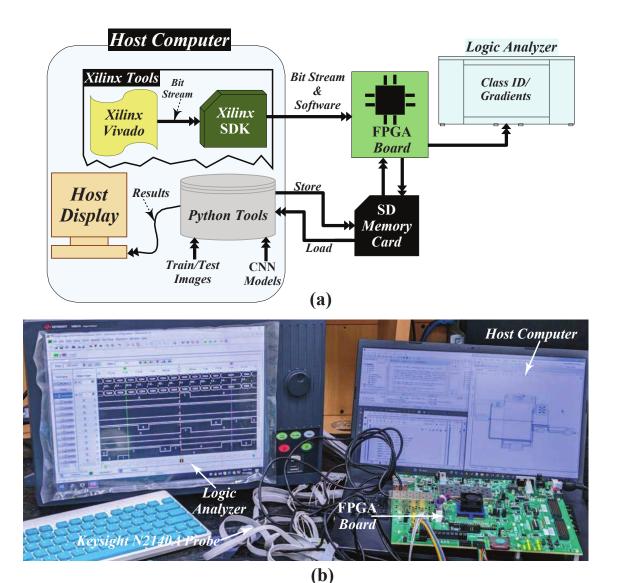

|   |                      |                                                    | 3.4.5.1 Hardware Test Setup and Valida   | ation Method                      | 59                                                                                                         |

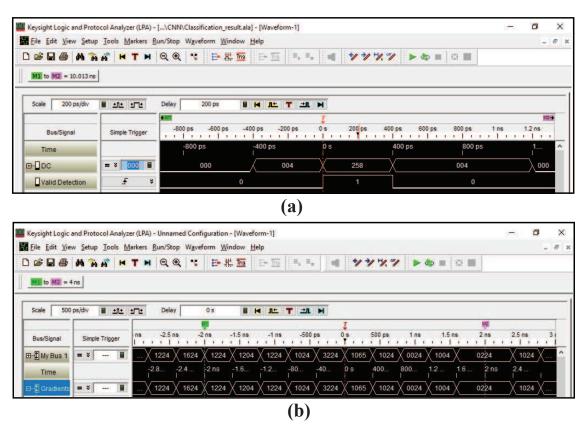

|   |                      |                                                    | 3.4.5.2 Experimental Results             |                                   | 61                                                                                                         |

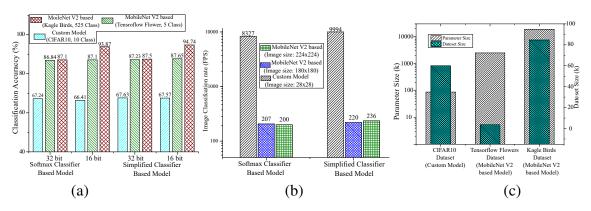

|   |                      | 3.4.6                                              | Accuracy of the Proposed CNN Accelerate  | tor                               | 62                                                                                                         |

|   | 3.5                  | Summ                                               | nry                                      |                                   | 63                                                                                                         |

|   |                      |                                                    |                                          |                                   |                                                                                                            |

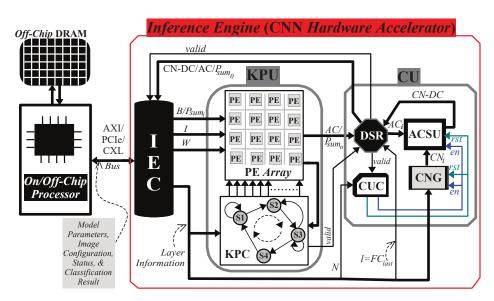

| 4 | Effic                | cient Cl                                           | IN Inference-Engine with Classify Unit   | hased on New Memory-              |                                                                                                            |

| 4 |                      |                                                    | NN Inference-Engine with Classify Unit   | based on New Memory-              | 65                                                                                                         |

| 4 | Sha                  | ring and                                           | Data-Reusing Techniques                  | ·                                 | <b>65</b>                                                                                                  |

| 4 | <b>Sha</b> : 4.1     | ring and                                           | Data-Reusing Techniques                  |                                   | 65                                                                                                         |

| 4 | Sha                  | ring and<br>Introde<br>Systen                      | Data-Reusing Techniques  action          |                                   | 65<br>69                                                                                                   |

| 4 | <b>Sha</b> : 4.1     | Introde<br>System<br>4.2.1                         | Data-Reusing Techniques  action          |                                   | <ul><li>65</li><li>69</li><li>69</li></ul>                                                                 |

| 4 | <b>Sha</b> n 4.1 4.2 | Introde<br>System<br>4.2.1<br>4.2.2                | Data-Reusing Techniques  action          |                                   | 65<br>69                                                                                                   |

| 4 | <b>Sha</b> n 4.1 4.2 | Introdu<br>System<br>4.2.1<br>4.2.2<br>Propos      | Data-Reusing Techniques  action          | ion Results and Compar-           | 65<br>69<br>69<br>70                                                                                       |

| 4 | <b>Sha</b> n 4.1 4.2 | Introdu<br>System<br>4.2.1<br>4.2.2<br>Proposisons | Data-Reusing Techniques  action          | ion Results and Compar-           | <ul><li>65</li><li>69</li><li>69</li><li>70</li><li>73</li></ul>                                           |

| 4 | <b>Sha</b> n 4.1 4.2 | Introdu<br>System<br>4.2.1<br>4.2.2<br>Propos      | Data-Reusing Techniques  action          | ion Results and Compar-           | <ul><li>65</li><li>69</li><li>69</li><li>70</li><li>73</li><li>73</li></ul>                                |

| 4 | <b>Sha</b> n 4.1 4.2 | Introdu<br>System<br>4.2.1<br>4.2.2<br>Proposisons | Data-Reusing Techniques  action          | ion Results and Compar-           | <ul><li>65</li><li>69</li><li>69</li><li>70</li><li>73</li><li>73</li><li>75</li></ul>                     |

| 4 | <b>Sha</b> n 4.1 4.2 | Introdu<br>System<br>4.2.1<br>4.2.2<br>Proposisons | Data-Reusing Techniques  action          | ion Results and Compar-           | <ul> <li>65</li> <li>69</li> <li>69</li> <li>70</li> <li>73</li> <li>73</li> <li>75</li> <li>77</li> </ul> |

| 4 | <b>Sha</b> n 4.1 4.2 | Introdu<br>System<br>4.2.1<br>4.2.2<br>Proposisons | Data-Reusing Techniques  action          | ion Results and Compar- re of KPU | 65<br>69<br>69<br>70<br>73<br>73<br>75<br>77                                                               |

| 4 | <b>Sha</b> n 4.1 4.2 | Introdu<br>System<br>4.2.1<br>4.2.2<br>Proposisons | Data-Reusing Techniques  action          | ion Results and Compar- re of KPU | <ul> <li>65</li> <li>69</li> <li>69</li> <li>70</li> <li>73</li> <li>73</li> <li>75</li> <li>77</li> </ul> |

|   |      |         | 4.3.2.2 CUC and CNG Micro-architectures                            | 4 |

|---|------|---------|--------------------------------------------------------------------|---|

|   |      |         | 4.3.2.3 ACSU Architecture                                          | 5 |

|   |      | 4.3.3   | Hardware Resources and Latency Analysis                            | 6 |

|   |      | 4.3.4   | ASIC Design and Comparison                                         | 8 |

|   | 4.4  | Hardw   | rare Development and Validation of Proposed CNN-Inference Engine 8 | 9 |

|   |      | 4.4.1   | Real-World Test Setup for Functional Validation                    | 1 |

|   |      | 4.4.2   | Model Compatibility                                                | 5 |

|   |      | 4.4.3   | Validation and Implementation Results                              | 5 |

|   |      |         | 4.4.3.1 MobileNet-V2 Implementation Flow                           | 5 |

|   |      |         | 4.4.3.2 ResNet50 Implementation Flow                               | 7 |

|   | 4.5  | Sumn    | nary                                                               | 8 |

| 5 | Unif | ied-CN  | N Accelerator for Training and Inference 10                        | 0 |

|   | 5.1  | Introdu | uction                                                             | 0 |

|   | 5.2  | Mathe   | matical Prerequisite and Research Problem                          | 3 |

|   |      | 5.2.1   | Mathematical Backgrounds of CNN Inference and Training 10          | 3 |

|   |      | 5.2.2   | Research Problem                                                   | 4 |

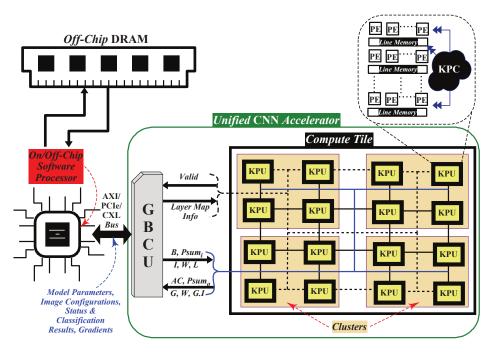

|   | 5.3  | Propos  | sed Technique and Hardware Architectures                           | 5 |

|   |      | 5.3.1   | System Model                                                       | 5 |

|   |      | 5.3.2   | Proposed Technique                                                 | 7 |

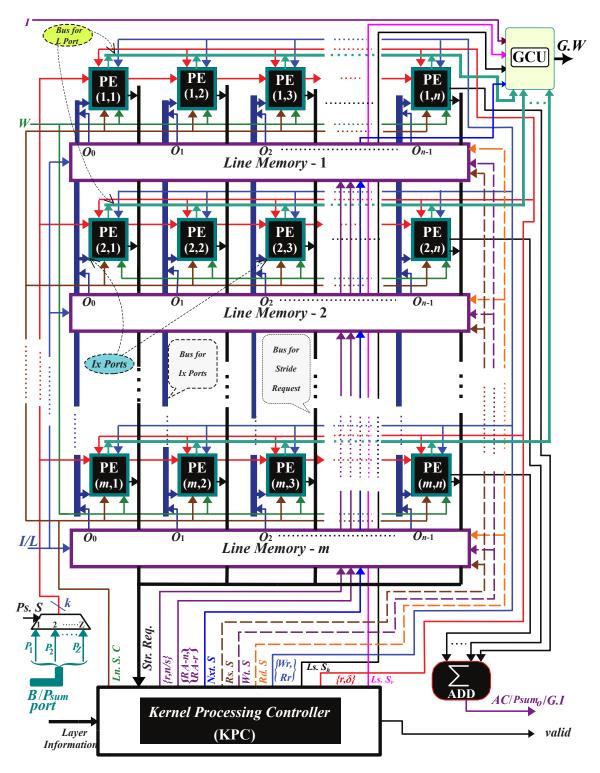

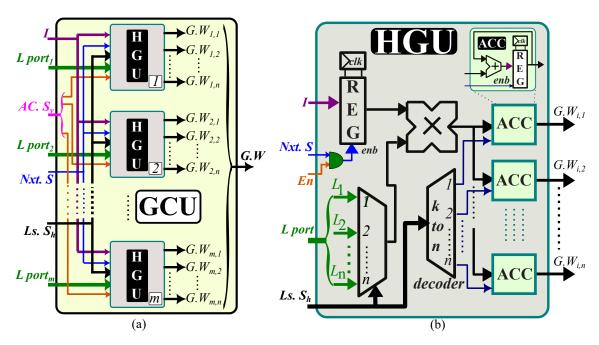

|   |      | 5.3.3   | Proposed Hardware Architectures                                    | 7 |

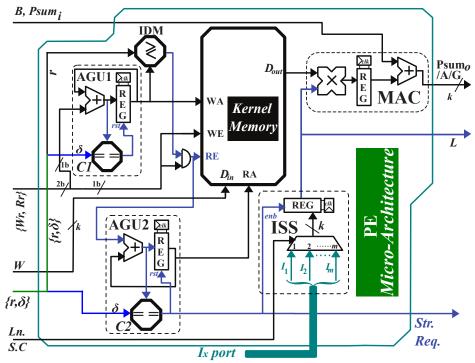

|   |      |         | 5.3.3.1 Energy-Efficient Micro-Architecture of KPU 10              | 7 |

|   |      |         | 5.3.3.2 Micro-architecture of PE                                   | 1 |

|   |      |         | 5.3.3.3 Micro-architecture of Line Memory                          | 3 |

|   |      |         | 5.3.3.4 Micro-architecture of Gradient Calculate Unit 11           | 3 |

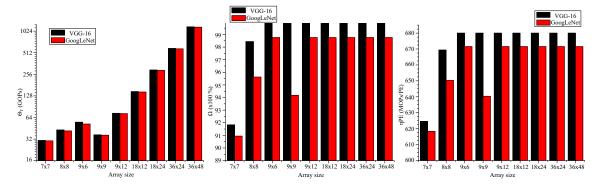

|   |      | 5.3.4   | Effect of PE-array Size on Efficiency                              | 5 |

|   | 5.4  | Hardw   | rare Implementation, Validation and Comparison                     | 6 |

|   |      | 5.4.1   | Test Setup for Hardware Validation                                 | 6 |

|   |      | 5.4.2   | Inference Implementation for Hardware Validation                   | 9 |

|   |      | 5 4 3   | Implementation of Training for Hardware Validation 12              | n |

|    |         | 5.4.4 Results and Comparison            | 123 |

|----|---------|-----------------------------------------|-----|

|    | 5.5     | Summary                                 | 126 |

| 6  | Sum     | amary, Conclusion and Future Directions | 127 |

|    | 6.1     | Thesis Summary                          | 127 |

|    | 6.2     | Conclusion                              | 130 |

|    | 6.3     | Future Directions                       | 131 |

| Bi | bliog   | raphy                                   | 133 |

| Li | st of 1 | Publications                            | 146 |

# **List of Figures**

| 1.1 | An overview of used cases for AI in different applications [5]               | 2  |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | Hierarchical relationship between artificial intelligence, machine learning, |    |

|     | neural networks, and deep learning. Each inner circle represents a subset of |    |

|     | the outer concept, with examples of models and methods associated at each    |    |

|     | level                                                                        | 4  |

| 1.3 | Illustration of Human Object Recognition vs. CNN Processing                  | 7  |

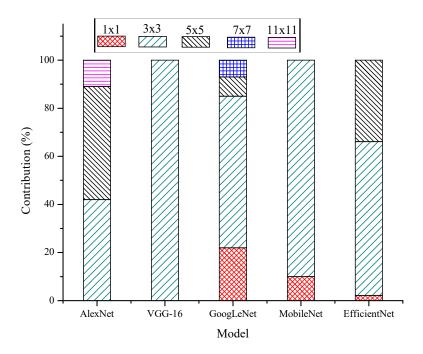

| 1.4 | Computations contributed by different kernel sizes in CNN models             | 9  |

| 1.5 | ImageNet classification accuracy versus network depth for major CNN ar-      |    |

|     | chitectures                                                                  | 13 |

| 1.6 | An overview of a distributed deep learning framework showing the flow of     |    |

|     | data from terminal devices to the cloud, where computation-intensive tasks   |    |

|     | are executed                                                                 | 14 |

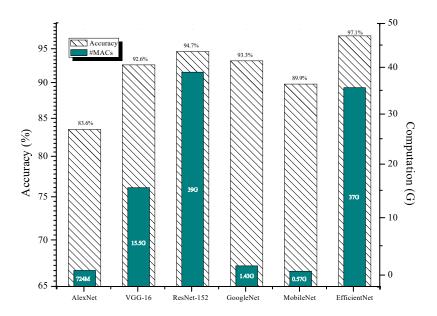

| 2.1 | Computation cost and accuracy of the state-of-the-art CNN models             | 25 |

| 2.2 | Computations contributed by different kernel sizes in CNN models             | 26 |

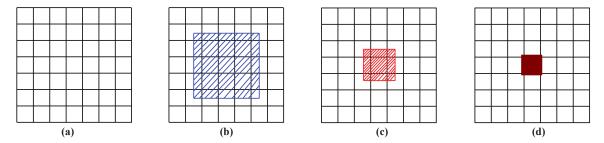

| 2.3 | Schematic representations of (a) a convolution processing unit for 7×7 ker-  |    |

|     | nels, (b) mapping 5×5 convolution, (b) mapping 3×3 convolution, and (c)      |    |

|     | mapping 1×1 convolution on 7×7 convolution processing units                  | 27 |

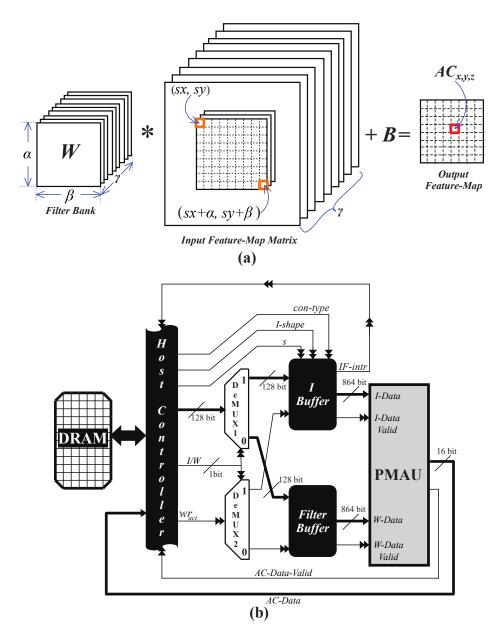

| 2.4 | (a) Schematic illustration of convolution process, and (b) proposed high-    |    |

|     | level of hardware accelerator to efficiently map different types of filters  | 29 |

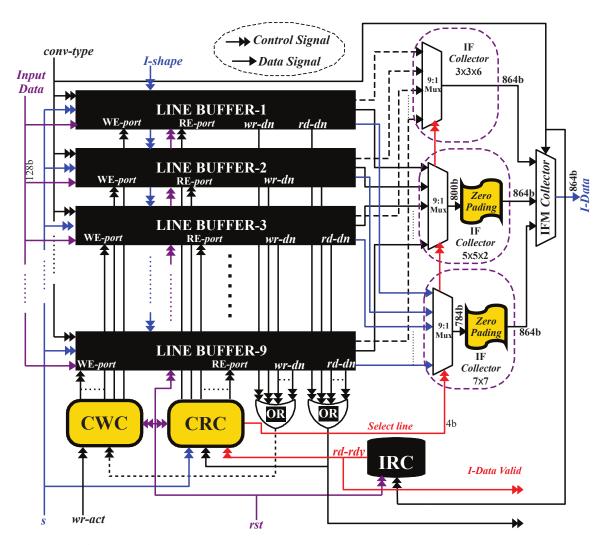

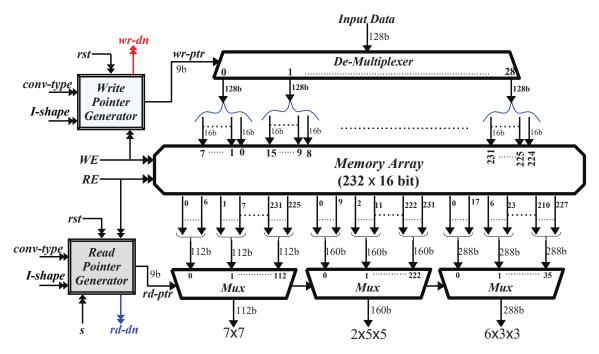

| 2.5 | Proposed VLSI architecture of <i>I Buffer</i> for the hardware accelerator   | 31 |

| 2.6 | Micro-architecture of line-buffer for the proposed <i>I Buffer</i> design    | 33 |

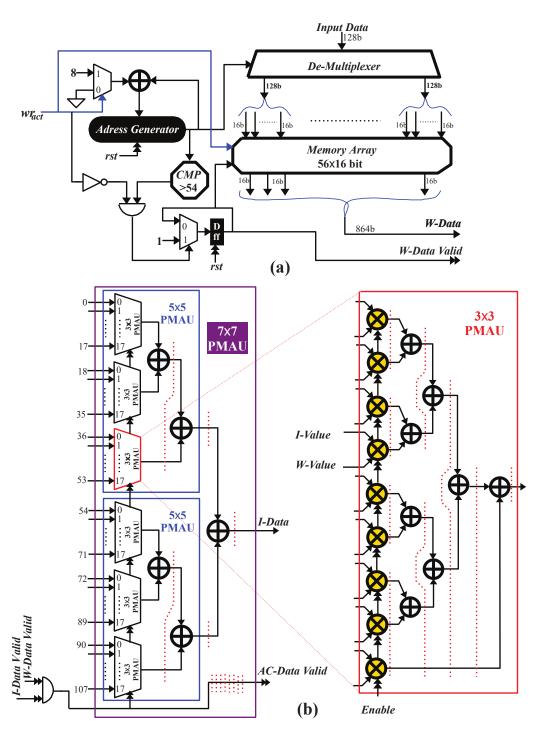

| 2.7 | Micro-architectures of (a) Filter Buffer and (b) PMAU for the proposed I         |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | Buffer design                                                                    | 34  |

| 3.1 | Schematic representation of the hardware level system using FPGA board           |     |

|     | and other supporting peripherals                                                 | 43  |

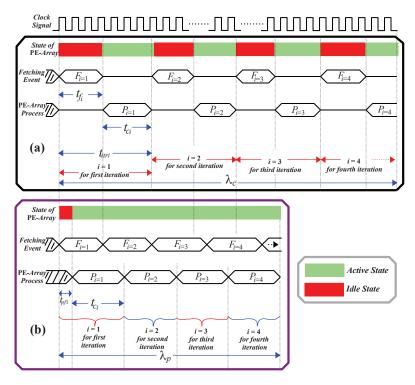

| 3.2 | Timing diagrams for (a) conventional and (b) proposed techniques                 | 47  |

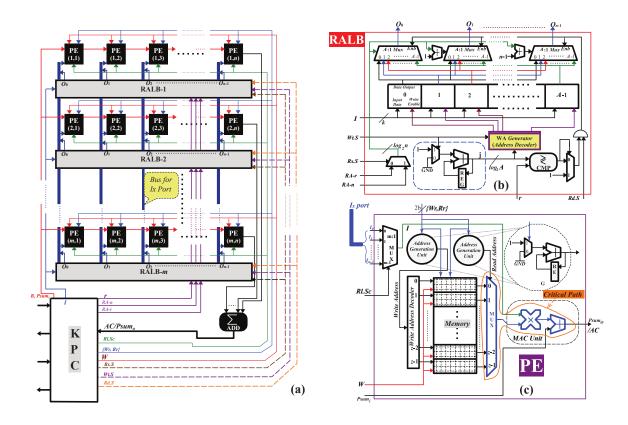

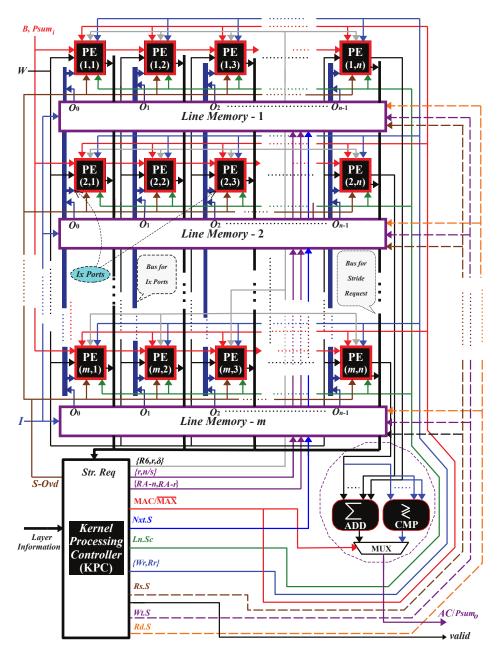

| 3.3 | (a) Proposed VLSI-architecture of CNN accelerator, (b) suggested internal        |     |

|     | micro-architecture of RALB, and (c) PE micro-architecture                        | 49  |

| 3.4 | Schematic representation of the suggested data-reusability process for 3×3       |     |

|     | PE array in CNN accelerator                                                      | 51  |

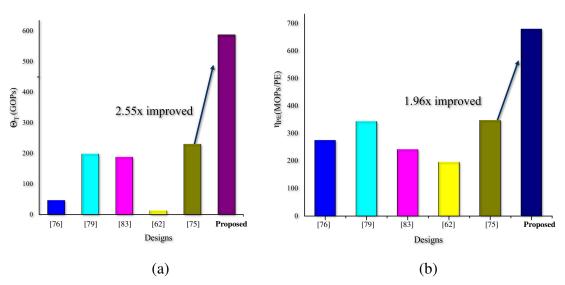

| 3.5 | Performance gain compared to state-of-the-art works. (a) Throughput $\Theta_T$ , |     |

|     | (b) Throughput density $\eta_{PE}$                                               | 55  |

| 3.6 | Various achievable values of throughput (Left), PE efficiency (Center), and      |     |

|     | throughput density (Right) using different sizes of PE-array in the proposed     |     |

|     | CNN accelerator for VGG-16 and GoogLeNet CNN models                              | 56  |

| 3.7 | (a) Schematic representation, and (b) real-world snapshot of the test setup      |     |

|     | for validating the proposed CNN accelerator prototype                            | 60  |

| 3.8 | Schematic representation of layer-wise processing of an image in the pro-        |     |

|     | posed CNN accelerator for GoogleNet model                                        | 61  |

| 4.1 | Overall architecture of an objection classification system based on the pro-     |     |

|     | posed CNN inference engine                                                       | 68  |

| 4.2 | Comparative accuracy and performance analyses of the proposed implementation     | on- |

|     | friendly algorithm for CNN inference engine                                      | 72  |

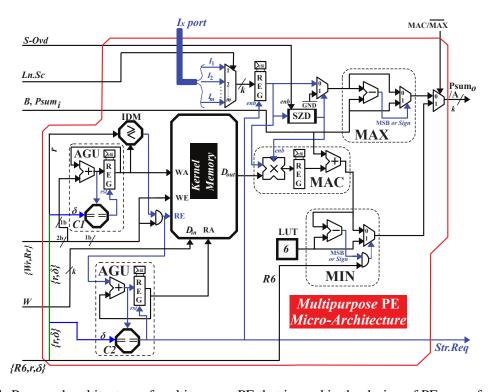

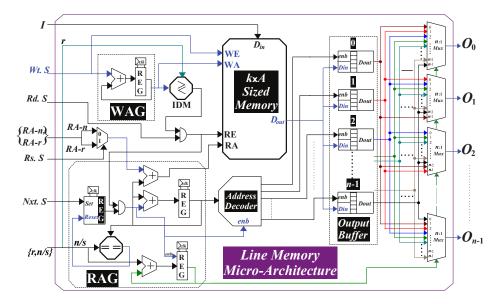

| 4.3 | Proposed hardware architecture of energy and memory efficient KPU                | 74  |

| 4.4 | Proposed architecture of multipurpose PE that is used in the design of PE-       |     |

|     | array for KPU                                                                    | 76  |

| 4.5 | Proposed architecture of single line-memory, used in the design of PE array      |     |

|     | for KPU                                                                          | 78  |

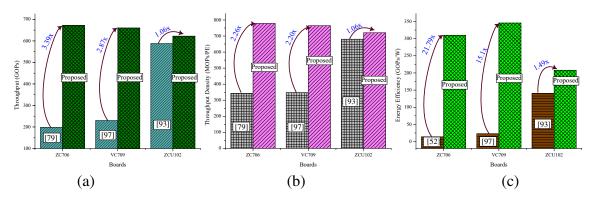

| 4.6 | Gains (a) throughput, (b) throughput density, and (c) energy efficiency of       |     |

|     | the proposed KPU compared to state-of-the-art works                              | 82  |

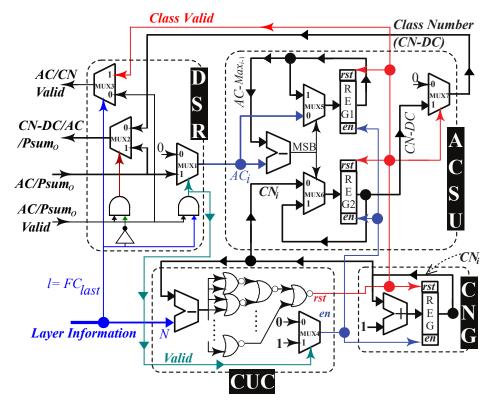

| 4.7  | Proposed micro-architecture of classify unit for the proposed CNN inference   |     |

|------|-------------------------------------------------------------------------------|-----|

|      | engine                                                                        | 86  |

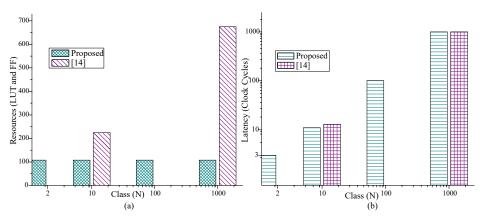

| 4.8  | Comparison analysis plots of (a) hardware resources and (b) latency, con-     |     |

|      | sumed by proposed and state-of-the-art CU architectures for different values  |     |

|      | of <i>N</i>                                                                   | 87  |

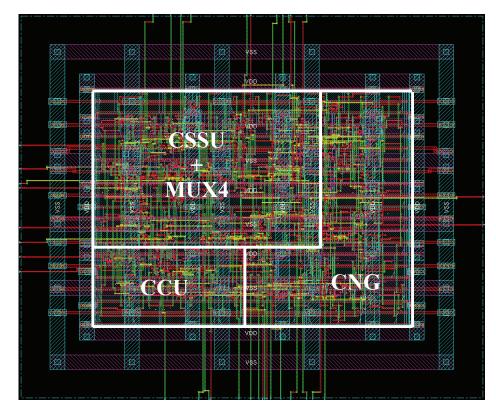

| 4.9  | Core ASIC layout (with 5 metal layers) of the proposed classify unit in 28    |     |

|      | nm-FDSOI technology node                                                      | 89  |

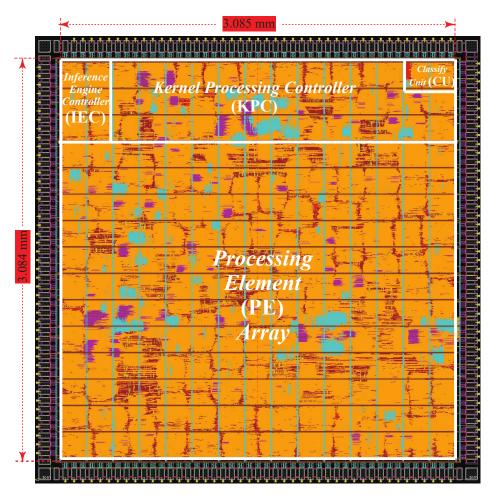

| 4.10 | ASIC chip-layout of the proposed inference engine for objection detection     |     |

|      | application in 28 nm FD-SOI technology node                                   | 91  |

| 4.11 | Real-world test setup of object detection system for functional validation of |     |

|      | the proposed CNN inference engine                                             | 92  |

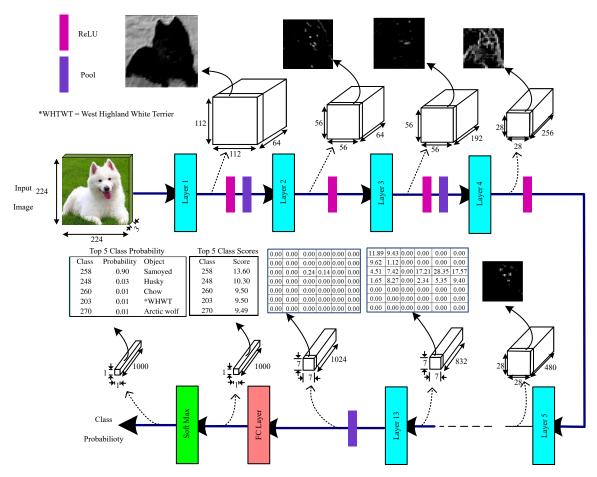

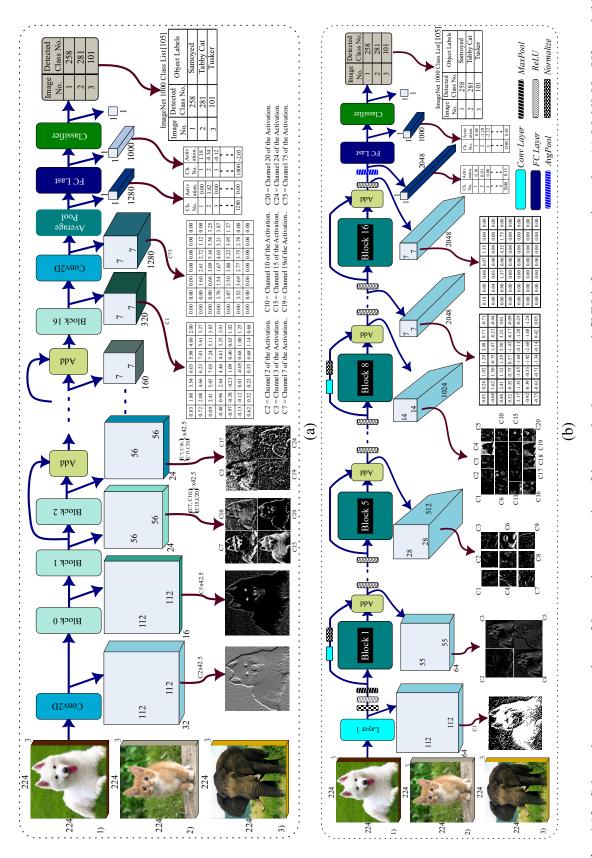

| 4.12 | Schematic representations of layer-wise processing of images in the pro-      |     |

|      | posed CNN inference engine using (a) MobileNet-V2, and (b) ResNet50           |     |

|      | models                                                                        | 94  |

| 5.1  | Overall system-level design of the proposed CNN engine for inference and      |     |

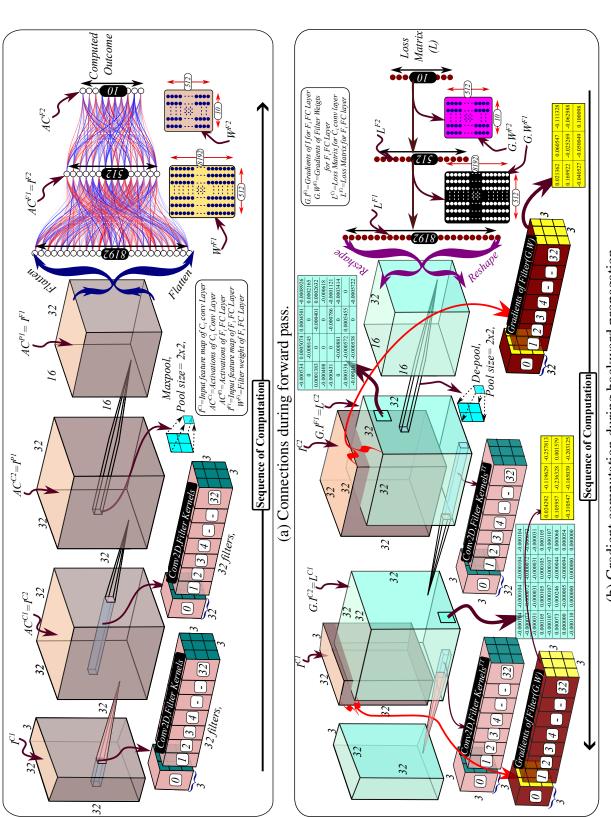

|      | training of CNN models                                                        | 106 |

| 5.2  | Proposed energy-efficient micro-architecture of KPU                           | 110 |

| 5.3  | Proposed micro-architecture of PE that is used in the design of PE-array for  |     |

|      | KPU                                                                           | 112 |

| 5.4  | Proposed (a) architecture of GCU and (b) micro-architecture of HCU            | 114 |

| 5.5  | (a) Schematic and (b) real-world snapshot of the test setup for the hardware  |     |

|      | validation of the proposed unified-CNN accelerator for inference and train-   |     |

|      | ing                                                                           | 115 |

| 5.6  | Measured outputs from the FPGA prototype of the proposed unified-CNN          |     |

|      | accelerator for (a) inference and (b) training processes                      | 117 |

| 5.7  | Schematic representations of layer-wise processing of images in the pro-      |     |

|      | posed unified-CNN accelerator during the forward pass of inference using      |     |

|      | VGG-16 CNN-model                                                              | 118 |

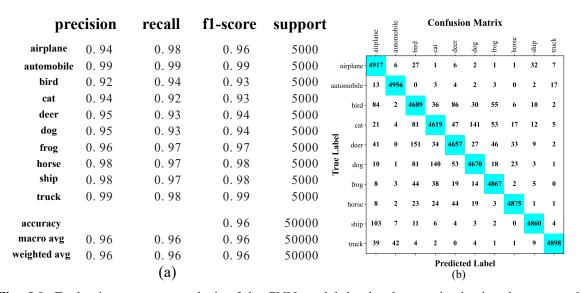

| 5.8  | Schematic representations of a custom CNN model for CIFAR10 data set.         | 121 |

| 5.9 | Evaluation accuracy analysis of the CNN-model that has been trained using    |     |

|-----|------------------------------------------------------------------------------|-----|

|     | the proposed unified-CNN engine: (a) precision, recall, and f1-score, and    |     |

|     | (b) confusion matrix                                                         | 123 |

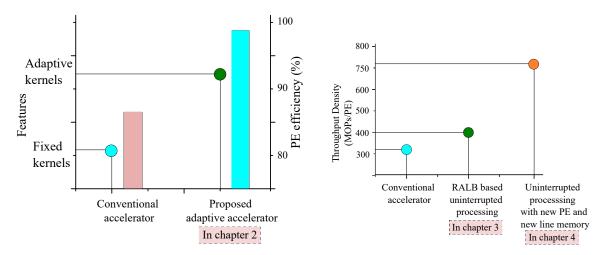

| 6.1 | PE efficiency comparison                                                     | 128 |

| 6.2 | Throughput density improvement                                               | 128 |

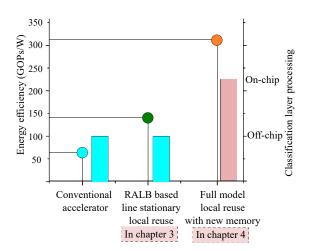

| 6.3 | Energy efficiency of baseline, locally reused, and fully reused CNN acceler- |     |

|     | ator architectures                                                           | 129 |

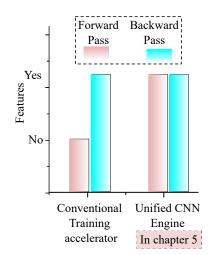

| 6.4 | Comparison of support for forward and backward pass in conventional and      |     |

|     | unified CNN training accelerators                                            | 129 |

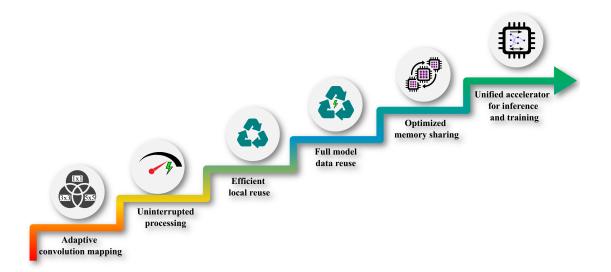

| 6.5 | Summary of architectural contributions across chapters showing progression   |     |

|     | from convolution mapping to unified training support                         | 130 |

# **List of Tables**

| 2.1 | Brief Summary of Contemporary CNN models                                   | 25  |

|-----|----------------------------------------------------------------------------|-----|

| 2.2 | Contribution of Different Filters in Total Computation of Various CNN Mod- |     |

|     | els                                                                        | 26  |

| 2.3 | Comparison with prior works                                                | 36  |

| 3.1 | FPGA and ASIC Implementation-Results Comparison of Proposed CNN            |     |

|     | Accelerator with Relevant State-of-the-Art Works                           | 53  |

| 4.1 | Comparison of Proposed KPU Implementations with Relevant State-of-the-     |     |

|     | Art Works                                                                  | 81  |

| 4.2 | Comparison of Proposed Classify Unit with Relevant State-of-the-Art FPGA   |     |

|     | based Works.                                                               | 87  |

| 4.3 | Comparison of Proposed Classify Unit with Relevant State-of-the-Art Works  |     |

|     | where all these Implementations are carried out in 28 nm-FDSOI Technol-    |     |

|     | ogy Node with 16 bits of Data Precision                                    | 90  |

| 4.4 | Implementation Results of the Complete Inference Engine in FPGA and        |     |

|     | ASIC platforms                                                             | 90  |

| 5.1 | Comparison of Proposed Unified CNN Accelerator Implementations with        |     |

|     | Relevant State-of-the-Art Works                                            | 124 |

## **Abbreviations**

#### *1-9*

**1D:** One **D**imensional.

**3D:** Three **D**imensional.

#### A

**ACCs: Acc**umulators.

ACSU: Activation Searching Unit.

**ADAS:** Advanced **Driver Assistance Systems**.

**AGU:** Address-Generation Units.

AI: Artificial Intelligence.

ASIC: Application Specific Integrated Circuit.

ASR: Automatic Speech Recognition.

AvgPool: Average Pool.

**AXI:** Advanced Extensible Interface.

#### $\boldsymbol{B}$

**BERT:** Bidirectional Encoder Representations from Transformers.

BNN: Boltzmann Neural Networks.

BRAM: Block RAM.

$\boldsymbol{C}$

**CE:** Compute Efficiency.

*CN-DC*: Class No. of the Detected object Class.

CNG: Class No. Generator.

CNNs: Convolutional Neural Networks.

**Conv**: Convolution.

**CORDIC:** Coordinate-Rotations Digital-Computer.

**CRC:** Current Read-Line-Select Controller.

CT: Compute Tile.

CU: Classify Unit.

CUC: Classify Unit Controller.

**CWC:** Current Write-Line-Select Controller.

$\boldsymbol{D}$

**DeMUX: De-MU**ltiple**X**er.

**DL:** Deep Learning.

DMA: Direct-Memory-Access.

**DRAM:** Dynamic Random-Access-Memory.

**DSR:** Data-&-Signal Router.

**DWC:** Depth-Wise Separable Convolution.

$\boldsymbol{E}$

**EDA:** Electronics-Design-Automation.

F

FC<sub>Last</sub>: Last Fully Connected.

**FDSOI:** Fully Depleted Silicon On Insulator.

**FP16:** 16-bit Fixed-Point Format.

**FPGAs:** Field-Programmable Gate Arrays.

#### G

*G*: Gradient.

**G.B:** Gradients for Bias Values.

**G.I:** Gradients of Input feature map.

**G.W:** Gradients of filter Weights.

GBCU: Global-Buffer cum Control Unit.

GCU: Gradient Compute Unit.

**GPT:** Generative Pre-training Transformer.

**GPU:** Graphic Processing Unit.

#### H

HDL: Hardware-Description-Language.

**HGU:** Horizontal Gradient-Compute Unit.

#### I

**I:** Input feature map.

**IDM:** Input Data Monitor.

**IEC:** Inference Engine Controller.

IF-intr: interrupt signal from IF buffer.

ILA: Integrated Logic Analyzer.

iMC: in-Memory Computation.

**IP:** Intellectual-Property.

**ISS:** Input Selection Switch.

#### K

KM: Kernel Memory.

**KPC:** Kernel Processing Controller.

**KPU:** Kernel Processing Unit.

#### L

L: Loss Matrix.

LLMs: Large Language Models.

*Ln.S.C*: Line-Selection Control-signal.

$Ls.S_h$ : horizontal Loss Selector.

Ls.  $S_{\nu}$ : vertical Loss Selector.

LUT: Look-Up Table.

### M

MAC: Multiply-And-Accumulate.

*MaxPool*: Max Pooling operation.

ML: Machine Learning.

MLP: MultiLayer Perceptrons.

MUX: MUltipleXers.

#### N

**NER:** Named Entity Recognition.

NLP: Natural Language Processing.

NN: Neural Networks.

*Nxt.S*: Next Stride signal.

#### 0

**OPs:** Operations Per second.

#### P

**PE:** Processing Element.

PMAU: Parallel Multiply-&-Add Unit.

**PMOD:** Peripheral-MODule interface.

**PWC:** Point-Wise Convolution.

#### R

**RAG:** Read Address Generator.

RALB: Random-Access Line-Buffer.

**Rd.S:** Read Selector.

*RdPtr*: Read Pointers.

rd-rdy: read ready signal.

**RE:** Read Enable signal.

**REG: REG**isters.

**ReLU:** Rectified Linear Unit.

**ReLU6:** A special **ReLU** that clips input values between 0 and 6.

**RGB:** Red Green Blue color.

**RL:** Reinforcement Learning.

RNN: Recurrent Neural Networks.

**Rs.S:** Select- for -Reuse signal.

#### S

**SD:** Secure Digital (Memory Card).

Str.Req: Stride Request signal.

SZD: Sign-And-Zero Detector.

#### T

**TPUs:** Tensor Processing Units.

TTS: Text- To -Speech.

#### W

WAG: Write Address Generator.

WE: Write Enable port.

$wr_{act}$ : write-activation signal.

*Wr*: Write command signal.

wr-dn: write-done indicator signal.

Wt.S: Write Selector.

## **Symbols**

- $\alpha$  Width of a kernel.

- $\hat{\alpha}$  Energy consumption associated with each  $\hat{a}$  type data movement.

- $\beta$  Height of a kernel.

- $\hat{\beta}$  Energy consumption associated with each  $\hat{b}$  type data movement.

- $\delta$  Index of the filter kernel.

- $\epsilon$  Energy efficiency, expressed as  $\epsilon = \Theta_T/W$ .

- $\eta_{MAC}$  Compute efficiency, calculated as the number of operations performed per MAC unit (ops/MAC).

- $\eta_{PE}$  Throughput density, given as the number of operations performed by a single PE per unit time (i.e. Ops/PE).

- $\eta_{PE-N}$  Hardware Efficiency at normalized clock frequency.

- $\gamma$  Depth of the filter kernel.

- $\hat{\gamma}$  Energy consumption associated with each  $\hat{c}$  type data movement.

- $\lambda_c$  Latency of conventional CNN accelerators, given as  $\lambda_c = \sum_{i=1}^{n} (t_{f_i} + t_{c_i})$ .

- $\lambda_p$  Latency of RALB based CNN accelerators, given as:  $\lambda_p = (\sum_{i=1}^n t_{c_i}) + t_{pf1}$ .

- Ω PE efficiency, represented by  $Ω = (N_{PE-util.}/N_{PE})$ .

- $\psi_m$  Energy required to move the data between the computation unit of PE and storage locations at different hierarchy. Expressed as  $\psi_m = a \cdot \alpha + b \cdot \beta + c \cdot \gamma$ .

- $\sigma$  Time efficiency, calculated as the ratio of time duration when PEs are active and total time duration required for the computation.

- *Rr*: Read signal from KPC for PE.

- $\Theta_T$  Computation throughput, given as  $\Theta_T = 2(N_{PE} \times f_{clk} \times \Omega \times \sigma)$  number of operations per second.

$\varepsilon_c$  Computation cost for each data which depends on the design logic and

its precision.

Number of horizontal strides to calculate G.I.

$FC_{last}$  Last fully connected layer.

A Width of each row of I.

â Number of times a data has been loaded from DRAM to GBCU.

$AC_{Max}$  Largest activation.

AC-Data Output feature-map matrix from PMAU.

AC Output activation values.

Bias values.

$\hat{b}$  Number of times the a data has been loaded from GBCU-to-RALB.

BF16 16 bit brain-float format.

$\hat{c}$  Number of times the a data has been loaded from RALB-to-PE.

$C_{\alpha\beta}$  Computation share contributed by each filter of size  $\alpha \times \beta$ , which is calculated

as  $C_{\alpha\beta} = (\mathcal{M}_{\alpha\beta}/\mathcal{M}_{tot}) \times 100 \%$ .

CN-DC Class id of detected object (classification result).

$CN-DC_{i-1}$  Class id of the object associated with  $AC_{Max_{i-1}}$ .

*conv-type* Control signal to indicate the type of convolution.

$f_{clk}$  Operating Clock frequency.

$F_i$   $i^{th}$  fetching event.

G.B Gradients for bias values.

G.I Gradients for input feature map.

G.W Gradients for filter weights.

I Input feature map.

*I-Data* Output bus of *I* buffer.

IRC I read-state controller.

*I-shape* Dimension of *I*.

$itr_i$ .  $i^{th}$  iteration.

I-W Control signal to chose between input feature-map and filter weight.

*l* Index of current layer.

L The loss matrix corresponding to a 3D filter.

M Number of items that can be stored in an RALB.

*m* Number of PEs in a rows.

$\check{M}$  Number of neurons in the  $FC_{last}$  layer.

$\hat{M} \times \hat{N} \times \hat{O}$  Dimensions of 3D loss matrix L.

$\mathcal{M}_{\alpha\beta}$  Number of MACs contributed by filters of size  $\alpha \times \beta$ .

$\mathcal{M}_{tot}$  Number of MACs contributed by all the filters of a model.

$\max\{I(x:\alpha,\ y:\beta,\ z)\}$  Maxpool: extraction of largest element from the  $\alpha\times\beta$  matrix

window of I with an origin at x, y.

$max\{0, I_{x,y,z}\}$  Perform ReLU on  $I_{x,y,z}$ .

*n* Number of PEs in a column.

N Total number of classes in the model.

$N_{PE}$  Total number of PEs available in the KPU.

$N_{PE-util.}$  Number of PEs utilized.

$n_l$  Number of iterations required for  $l^{th}$  layer.

$O_i$   $i^{th}$  output port of the line memory.

$P_i$   $i^{th}$  Process event.

$Pr_i$  Probability score of  $i^{th}$  class.

Psum Partial sum (Incomplete AC).

*Psum*<sub>i</sub> Input partial sum.

*Psum*<sub>o</sub> Output partial sum.

$Q_{n.m}$  n+m bit fixed point representation with n bits for integer part and

*m* bits for the fractions.

$r_l$  Minimum number of data items that are required to begin the processing

of  $l^{th}$  layer.

s Stride size.

S-Ovd Controll signal to override SZD for first layer of the model.

t Duration of computation.

$t_{c_i}$  Data computation time of  $itr_i$ .

$t_{f_i}$  Data fetching time for  $itr_i$ .

$t_{itr_i}$  Total time for  $itr_i$ , computed as  $t_{itr_i} = t_{f_i} + t_{c_i}$ .

$t_{pf_i}$  Pre-fetch duration to load minimum number of data for  $itr_i$ .

U Activity rate of PEs that is given by  $U=t_{ci}/t_{itr_i}$ .

W Filter weights.

W Average power consumption, computed as  $W = (\varepsilon_c + \psi_m)/t$ .

$wr_{act}$  Write-activation signal.

wr-dn Write-done signal.

wr-ptr Write pointer.

x,y,z Lateral, vertical and spatial position of the AC value that is being processed.

xx Current position of the data in lateral axis, that is being processed during current stride.

yy Current position of the data in vertical axis, that is being processed during current stride.

z Number of filter weights that can be stored in the kernel memory inside PE.

zz Current position of the data in spatial axis, that is being processed during current stride.

#### Chapter 1

#### Introduction

#### 1.1 Artificial Intelligence

Artificial intelligence (AI) is a transformative field of computer science that focuses on developing systems capable of simulating human intelligence. These systems are designed to perform cognitive tasks such as learning, reasoning, problem-solving, perception, decision-making, and language understanding. Over the past few decades, AI has progressed from theoretical concepts to real-world applications, shaping various industries and redefining technological possibilities [1].

The origins of AI can be traced back to the mid 20<sup>th</sup> century, with early concepts emerging from philosophy, mathematics, and neuroscience. Alan Turing's foundational work on computation and intelligence laid the groundwork for the field, proposing the idea that machines could mimic human cognitive functions [2]. The development of symbolic AI in the 1950s and 1960s introduced rule-based systems designed to simulate logical reasoning [2]. However, these early AI systems were limited by their reliance on manually coded knowledge, which restricted their adaptability to complex real-world scenarios [3].

The evolution of AI has been heavily influenced by advances in computational power, data availability, and algorithmic improvements. The late 20<sup>th</sup> century witnessed the rise of machine learning (ML), shifting the focus from hand-crafted rules to data-driven learning techniques [4]. This transition enabled AI systems to learn patterns from large datasets and improve performance over time without explicit programming. The advent of deep learn-

ing (DL) in the early 21<sup>st</sup> century further revolutionized AI, enabling models with multiple layers of artificial neurons to achieve unprecedented accuracy for image and speech recognition [5].

In present time, AI has been deeply embedded in everyday life, powering applications such as virtual assistants, recommendation systems, autonomous vehicles, healthcare diagnostics and many more. The field continues to evolve with advancements in reinforcement learning, natural language processing, and computer vision [6].

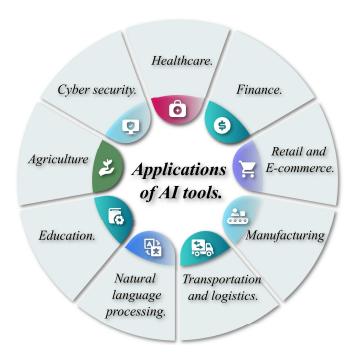

Fig. 1.1: An overview of used cases for AI in different applications [5].

#### 1.2 Applications and Impact of AI

AI has become a key driver of innovation, reshaping industries and everyday life by processing massive datasets, recognizing patterns, and supporting intelligent decision-making. Its applications span healthcare, finance, commerce, manufacturing, transportation, education, agriculture, and cybersecurity, where it continues to enhance efficiency, accuracy, and automation across diverse domains [6, 7].

In healthcare, AI enhances personalized medicine by analyzing genetic profiles and clinical data to tailor treatments for individual patients. Predictive analytics assist doctors in

identifying high-risk patients, monitoring vital signs, and detecting anomalies. It also supports medical imaging analysis, accelerates drug discovery, and enables remote patient monitoring, thereby improving clinical outcomes while reducing costs [8,9].

In finance, AI does real-time fraud prevention by meticulously analyzing streams of transactional data to detect and block suspicious activities before they escalate. It also powers algorithmic trading, ensuring rapid order execution and the dynamic optimization of investment portfolios. In addition, AI can improve credit scoring, risk assessment, and personalized financial advisory services, making financial systems more secure and efficient [10, 11].

AI also plays a transformative role in retail and e-commerce, where it powers recommendation systems, demand forecasting, and inventory optimization. By predicting customer behavior and enabling dynamic pricing, it enhances supply chain efficiency while creating highly personalized shopping experiences [12, 13].

In manufacturing, AI enhances productivity through intelligent robotics, predictive maintenance, and adaptive process control. Automated quality inspection ensures consistency, while advanced decision-making systems reduce downtime and operational costs, making industries more flexible and resilient [5, 14].

Transportation and logistics are being reshaped by AI. Self-driving cars utilize AI-powered sensors, computer vision, and deep learning models to perceive their surroundings, make decisions, and navigate safely [15]. AI-based advanced driver-assistance systems (ADAS) improve road safety, while route optimization and intelligent traffic management enhance efficiency in logistics and urban mobility [16, 17].

Another major area is natural language processing (NLP), where AI enables real-time translation, chatbots, and sentiment analysis. These applications improve accessibility and customer service, while also allowing organizations to extract insights from vast collections of unstructured text [18].

Also, in education, AI can personalize learning experiences through adaptive learning platforms and intelligent tutoring systems that respond to student needs. Automated grading reduces routine workload for teachers, enabling them to focus on more impactful educational tasks [4].

AI is equally important in agriculture, where precision farming techniques rely on AI to monitor crop health, predict yields, and optimize the use of water and fertilizers. These innovations improve productivity and contribute to sustainable agricultural practices [19].

Another critical domain is cybersecurity, where AI enhances protection against cyber threats by detecting anomalies, predicting attack patterns, and automating incident responses. These systems provide stronger defense mechanisms for safeguarding sensitive data and critical infrastructures in real time [20].

Beyond these, AI is finding applications in areas such as surveillance, defense, creative industries, and many emerging fields that are still unfolding. The breadth of its impact illustrates how AI continues to reshape societies by enhancing decision-making, automating complex tasks, and unlocking new opportunities for innovation [1,21].

Despite their diversity, these applications are ultimately grounded in a set of core AI components like *machine learning* (ML), *neural networks* (NN), *deep learning* (DL), *natural language processing* (NLP), *reinforcement learning* (RL), etc., that collectively provide the foundation for intelligent behavior. A closer look at these key components will help clarify how AI systems achieve such versatility, which has been discussed in the following section.

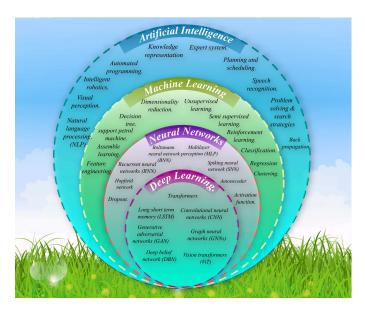

**Fig.** 1.2: Hierarchical relationship between artificial intelligence, machine learning, neural networks, and deep learning. Each inner circle represents a subset of the outer concept, with examples of models and methods associated at each level.

#### 1.3 Key Components of AI

The relationship among AI, ML, NN, and DL can be better understood through a layered view, as illustrated in Fig. 1.2. This nested structure clarifies how different models and techniques are interrelated across levels of abstraction and complexity. AI is built on a set of interrelated components that collectively enable machines to learn, reason, perceive, and act in ways similar to human intelligence. Among these, ML forms the foundation, allowing systems to identify patterns and make predictions from data [4]. As illustrated in Fig. 1.2, ML encompasses various paradigms such as supervised, unsupervised, and reinforcement learning, each enabling automated knowledge extraction from different types of datasets.

DL, a specialized subset of ML, employs multi-layered neural networks to achieve superior performance in complex tasks such as image recognition, speech processing, and natural language understanding [3, 5]. At the core of DL are NNs, computational models inspired by the human brains interconnected neurons. NNs are particularly effective at learning non-linear relationships, with architectures ranging from feedforward multilayer perceptrons to recurrent, convolutional, and graph-based variants. Convolutional Neural Networks (CNNs), in particular, have revolutionized computer vision applications by automatically extracting spatial features from raw data, making them highly effective for image classification, object detection, and segmentation [22].

Beyond ML and DL, other AI components provide complementary capabilities. NLP enables machines to interpret and generate human language [18], while RL focuses on agents that learn optimal strategies by interacting with dynamic environments [21]. *Computer vision* (CV) interprets visual information for recognition and perception tasks, and *expert systems* encode domain-specific rules for automated decision-making [23].

As AI continues to advance, the demand for efficient computational resources grows, leading to the development of specialized hardware accelerators. The next sections will explore the role of hardware in AI, particularly in the optimization of deep learning workloads and the design of efficient CNN accelerators.

#### 1.4 Motivation for CNN-Centric Hardware Acceleration

Within the diverse spectrum of AI techniques, several models have played central roles at different stages of development. Early approaches such as expert systems and rule-based reasoning demonstrated how symbolic logic could capture human expertise, yet they lacked scalability and adaptability in handling unstructured data [23]. Feedforward multilayer perceptrons improved upon this by learning patterns directly from data, but their fully connected nature led to a prohibitive number of parameters and limited capacity to exploit structural correlations.

Recurrent Neural Networks (RNNs) and their variants extended learning to sequential data, showing notable success in speech and language processing. However, their training suffers from vanishing gradients, long convergence times, and limited parallelization [3], constraining their scalability for modern large-scale applications. Similarly, the reinforcement learning has been proven to be powerful for decision-making tasks but is less effective in perception-heavy domains without integration with deep architectures.

By contrast, CNNs introduced two critical architectural advances: local connectivity and weight sharing, that drastically reduce parameter counts while preserving the ability to capture hierarchical features. This design enables CNNs to efficiently learn from spatial and temporal correlations in data, making them uniquely suited for image recognition, object detection, medical imaging, and other perception-driven applications [5,22,24]. Their layered feature hierarchy mirrors aspects of human perception, progressing from edges and textures to higher-level semantic features, which has driven their dominance in computer vision and beyond.

CNNs have also demonstrated versatility, extending beyond vision to speech recognition, natural language processing, and bioinformatics, underscoring their robustness across AI domains [3]. While newer architectures such as transformers are gaining prominence, CNNs remain indispensable due to their computational efficiency, scalability, and the maturity of the supporting ecosystem. For these reasons, CNNs are chosen as the focal point of this thesis, with a particular emphasis on designing hardware-efficient solutions to address their computational challenges.

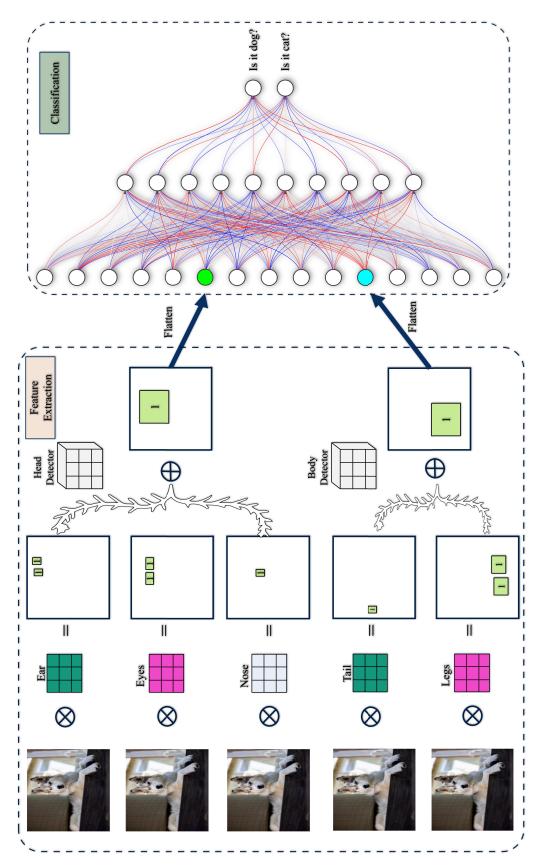

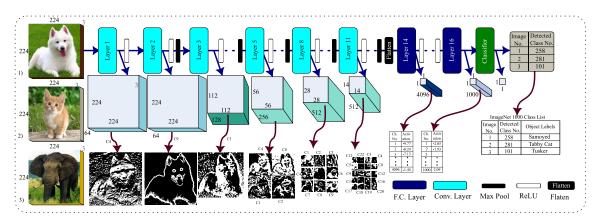

Fig. 1.3: Illustration of Human Object Recognition vs. CNN Processing.

# 1.5 Convolutional Neural Networks: From Intuition to Implementation

## 1.5.1 Human's Object Identification versus CNN Working Mechanism: An Analogy

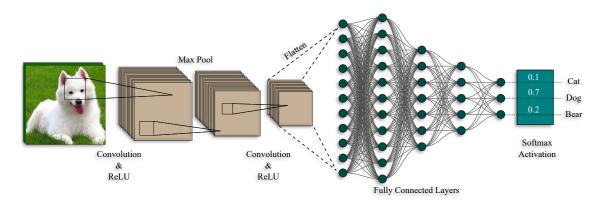

To design an effective CNN accelerator, we first need to understand the way a CNN model works. Fig. 1.3 provides an analogy between the way humans identify objects and the functioning of a CNN. When humans identify an object, such as a dog, we rely on recognizing distinct features ears, eyes, nose, tail, and legs and their relative positions. If these features match our internal concept of a dog, we classify the object accordingly.

Now, imagine a system with specialized "filters" designed to detect each of these features. For example, one filter might look for ears, another for eyes, and another for the nose, and so on as shown in Fig. 1.3. Some filters might even focus on combinations of features like ears, eyes, and nose to detect the head while others could detect the body, such as the legs and tail. This hierarchical approach mirrors the following step by step workings of a CNN model.

#### 1. Feature Extraction through Filters (Convolutional Layers):

- CNNs apply small, learnable filters (kernels) across the image to detect low-level patterns like edges, textures, and simple shapes, similar to how we check for features like ears, eyes, and nose.

- In the initial layers, filters capture basic visual elements without forming an understanding of the entire object.

#### 2. Building Higher-Level Representations (Deeper Convolutional Layers):

- When we combine features (ears, eyes, nose) to identify the head of a dog, deeper layers of the CNN combine low-level patterns to form more complex structures.

- Intermediate layers might detect partial structures (like a dog's head or body), which later layers use to recognize the full object.

#### 3. Object Classification (Fully Connected Layers & Decision Making):

- Once the CNN layers have identified key features and their arrangements, the network assigns confidence scores to different possible objects.

- Similar to how humans make a decision based on the overall arrangement of features, CNNs classify the object based on learned patterns.

This process closely mimics human analysis of visual information. However, unlike humans, CNNs learn which features to detect from large datasets, automatically discovering the most useful filters and patterns for distinguishing among different objects.

Fig. 1.4: Computations contributed by different kernel sizes in CNN models.

### 1.5.2 Understanding CNNs: A Hierarchical Approach to Image Recognition

A CNN processes images in a hierarchical fashion, progressively extracting features at various levels of abstraction. This approach is analogous to human object recognition, where individual features are first identified, then combined to form a complete understanding of the object. Fig. 1.4 provides a visual representation of one such CNN model.

The process starts at the input layer, where an image is represented as a three-dimensional tensor with dimensions  $H_i \times W_i \times C_i$ , where  $H_i$ ,  $W_i$ , and  $C_i$  represent image-height, imagewidth and number of channels, respectively, three for an RGB image.

#### 1.5.2.1 Feature Extraction: Convolutional Layers

CNNs utilize convolutional layers to extract spatial features. Small filters (kernels) of size  $k \times k$  slide over the input image, computing dot products between filter values and local image regions. This operation generates feature maps, highlighting significant image structures. Early layers capture low-level features like edges and textures, while deeper layers extract higher-level representations, such as object parts (eyes, nose, ears for a dog).

In the convolution (*Conv*) layer of CNN, each element of the output feature map is computed as

$$AC_{x,y,z,\delta} = \sum_{a=1}^{\alpha} \sum_{b=1}^{\beta} \sum_{c=1}^{\gamma} \left( W_{a,b,c,\delta} \times I_{xx,yy,zz} \right) + B_{\delta}.$$

$$(1.1)$$

In the above expression, AC, W, I, and B denote output activation, filter weight, input feature-map, and bias values, respectively. Likewise, x, y, z and  $\delta$  represent the positions of current value of output feature map over its four different dimensions. In addition, xx, yy, and zz are three dimensional positions of the current value of input feature map which is being processed. These values are computed as  $xx = (s \times x + a)$ ;  $yy = (s \times y + b)$ ;  $zz = (s \times z + c)$  where s denotes the stride size. Furthermore,  $\alpha, \beta, \gamma$  and  $\delta$  are the sizes of four different dimensions of filters of a layer. Thus,  $\alpha = \beta = 3$  for  $3 \times 3$  convolution and  $\alpha = \beta = 5$  for  $5 \times 5$  convolution.

#### 1.5.2.2 Non-Linearity: Activation Function

After convolution, an activation function, typically the rectified-linear-unit (*ReLU*), is applied to introduce non-linearity. *ReLU* is defined as:

$$AC_{x,y,z} = max\{0, I_{x,y,z}\}$$

(1.2)

This non-linearity allows the network to learn complex patterns by discarding negative values and retaining positive feature responses.

On the other hand, some CNN models with lower bit precision [25] use a special type of *ReLU* called *ReLU6* wherein, network discards negative values and retaining positive

feature responses. However, if the numerical value of the positive feature responses is more than 6, they are clipped to 6. Operation of such *ReLU6* operation can be expresses as:

$$AC_{x,y,z} = min\{max\{0, I_{x,y,z}\}, 6\}$$

(1.3)

#### 1.5.2.3 Dimensionality Reduction: Pooling Layers

To enhance computational efficiency and robustness, CNNs employ pooling layers. The most common method is maxpool, which selects the maximum value from non-overlapping regions of size  $\alpha \times \beta$ , where  $\alpha$  and  $\beta$  are the dimensions (height and width, respectively) of the pool kernel. This reduces spatial dimensions while preserving the most important features, helping achieve translation invariance and enabling CNNs to recognize objects despite minor shifts or variations in the image. Max-pooling is mathematically expressed as:

$$AC_{x,y,z} = \max\{I(x:\alpha, y:\beta, z)\}$$

(1.4)

where  $max\{I(x:\alpha, y:\beta, z)\}$  denotes the extraction of largest element from the  $\alpha \times \beta$  matrix window with an origin at (x, y) inside the  $z^{th}$  channel of I.

Some models [25], [26] also use average pooling (*avgpool*) wherein, the average of all elements of the  $\alpha \times \beta$  region is taken, instead of taking only the maximum value. Such *avgpool* operation can be expressed as :

$$AC_{x,y,z} = \frac{\sum_{x}^{+\alpha} \sum_{y}^{+\beta} I_{x,y,z}}{\alpha \times \beta}$$

(1.5)

#### 1.5.2.4 Higher-Level Feature Representation

As the network progresses through deeper convolutional and pooling layers, feature maps are further refined to detect more abstract structures, such as the overall shape of an object. This enables the network to develop a hierarchical understanding of the image, similar to how humans combine individual components to recognize an object.

#### 1.5.2.5 Classification: Fully Connected Layers and Output

Once feature extraction is complete, the feature maps are flattened into a one-dimensional vector and passed to fully connected (FC) layers. For FC layers, each element of AC is the weighted sum of all elements of I and their corresponding biases. This operation is mathematically expressed as

$$AC_{x} = \sum_{n=1}^{N} I_{n} \times W_{n,x} + B_{x}.$$

(1.6)

These FC layers learn relationships between the extracted features, with the final output layer using a softmax activation function to produce a probability distribution across different object classes:

$$Pr_i = \frac{e^{CS_i}}{\sum_{j}^{N} e^{CS_j}} \tag{1.7}$$

Here,  $CS_i$  network's score for class i. AC from the last FC ( $FC_{last}$ ) layer is given to softmax function as the class score (CS).  $Pr_i$  represents the network's score and probability for class i, respectively. The class with highest probability is then selected as the predicted label.

CNNs follow a structured approach for object recognition, starting with simple feature detection and progressing to complex pattern recognition. Such hierarchical method mirrors human perception, where objects are identified by combining distinct features. By automating the feature extraction and classification process, CNNs achieve profound accuracy in image recognition tasks.

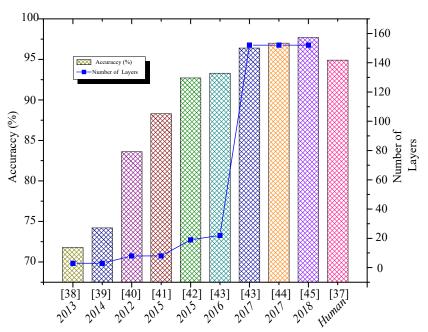

Fig. 1.5: ImageNet classification accuracy versus network depth for major CNN architectures.

#### 1.6 Accuracy and Complexity Trade-offs in AI Models

In recent years, AI models especially deep-convolutional neural networks have demonstrated remarkable improvements in accuracy and generalization, making them highly suitable for the deployment of high-stakes domains such as healthcare, autonomous vehicles, and surveillance systems [5], [27]. These models have evolved from relatively shallow architectures, like AlexNet [28] in 2012-13, to extremely deep and sophisticated designs such as ResNet [29] and SENet [30], which incorporate over 150 layers to extract hierarchical features from data. As depicted in Fig. 1.5, CNN models have not only improved consistently in performance but, in some cases, have surpassed human-level accuracy in visual recognition tasks [31]. This trend underscores the increasing reliability of AI in perception tasks. However, it also reflects a growing complexity in model architecture, which presents challenges in terms of computational cost, energy efficiency, and interpretability. The trade-off between performance and complexity remains a central concern in the design and application of modern AI systems.

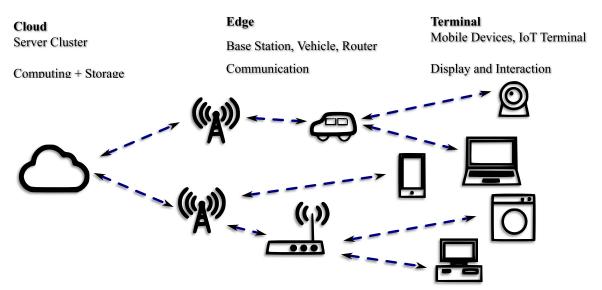

**Fig.** 1.6: An overview of a distributed deep learning framework showing the flow of data from terminal devices to the cloud, where computation-intensive tasks are executed.

With the increasing complexity, modern deep learning models, especially deep neural networks, have become increasingly computationally intensive, requiring substantial processing power and memory. These requirements often exceed the capabilities of mobile or embedded devices. To address this limitation, intelligent systems are now commonly deployed in a distributed architecture involving three main layers: terminals, edge, and cloud. User-end devices such as smartphones and IoT sensors (terminals) are primarily responsible for data collection and interface tasks. The data is then transmitted to more capable cloud servers via intermediate edge devices such as routers or base stations. In the cloud, largescale computational resources perform the main inference and analysis operations. The results are subsequently returned to the terminal for real-time interaction. Fig. 1.6 shows an overview of such distributed deep learning framework depicting the flow of data from terminal devices (e.g., mobile phones, sensors) through edge infrastructure to the cloud, where computation-intensive tasks are executed. Such model enables services like voice assistants (e.g., Siri or Alexa) and smart applications (e.g., Google Lens) to operate efficiently despite hardware constraints at the user level. However, this distribution of computation introduces new challenges related to latency, bandwidth usage, and data privacy, which have become critical considerations in system design [36], [37], [38].

# 1.7 CNN Hardware Accelerators: Addressing Computational Challenges in AI

The rapid advancement of AI, particularly in deep learning, has led to an increasing demand for high-performance computation. CNNs are widely used in image processing, computer vision, and various other AI applications, require significant computational resources due to their reliance on large-scale matrix operations, convolutional computations, and iterative optimization techniques. General-purpose processors are often inefficient in handling these tasks due to their sequential processing nature and limited parallelism. While graphics processing units (GPUs) offer substantial parallelism, however, they face limitations in power efficiency and flexibility, making the need of dedicated AI accelerators more pressing [22, 39].

The inefficiencies of traditional architectures stem from their inability to efficiently execute the massive parallel computations required for CNN training and inference. Many AI workloads, particularly those deployed in real-time applications and edge devices, operate under strict power and thermal constraints. Conventional computing architectures struggle with balancing performance and energy efficiency, necessitating the development of specialized hardware solutions on application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs) platforms [40]. These accelerators improve performance by minimizing redundant computations, optimizing data movement, and leveraging hardware parallelism.

CNN accelerators are designed to optimize key operations commonly found in deep learning models:

- Matrix Multiplication and Convolutions: CNNs heavily rely on these operations, which can be significantly accelerated using dedicated hardware architectures [41].

- Quantization and Sparsity Exploitation: Specialized AI accelerators incorporate

techniques such as reduced precision computation like 8 or 16 bit fixed point representation instead of 32 bit floating point representation of numbers, and sparsity-aware

processing to enhance efficiency while maintaining accuracy [42].

• **Memory Hierarchy Optimization:** AI accelerators implement optimized memory hierarchies, including high-bandwidth on-chip caches and dataflow architectures, to minimize latency and improve computational throughput [43].

Additionally, real-time AI applications, such as autonomous vehicles, robotics, and medical diagnostics, demand ultra-low latency processing. Traditional processors struggle to meet these stringent timing constraints, making dedicated CNN hardware accelerators essential. These accelerators employ efficient pipeline architectures and memory optimizations to ensure high-speed computation [5].

Furthermore, scalability is another critical factor in AI acceleration. As deep learning models grow in complexity, conventional architectures face bottlenecks due to memory bandwidth limitations and inefficient resource utilization. AI hardware accelerators address these challenges by offering:

- Scalable Architectures: AI-optimized hardware, including tensor processing units (TPUs) and advanced FPGAs, enables efficient multi-chip scalability, allowing large-scale CNN training and inference [44].

- **Reconfigurability:** FPGAs provide adaptable hardware implementations, making it possible to support different CNN models and applications without requiring costly new chip fabrication [45].

On the other hand, the economic viability of large-scale AI deployment depends on cost-effective and energy-efficient hardware solutions. General-purpose computing clusters incur high operational costs due to inefficiencies in power consumption and hardware utilization. AI accelerators improve cost efficiency by enhancing processing throughput and reducing power consumption, making large-scale CNN applications more practical and accessible [46].

Given the growing complexity of CNN models and the increasing need for efficient, real-time processing, the development of specialized hardware accelerators is essential. By addressing the limitations of traditional processors, CNN accelerators significantly enhance computational efficiency, scalability, and power optimization. This motivation underpins the

necessity of designing CNN hardware accelerators to meet the ever-evolving demands of AI applications across cloud computing, edge devices, and real-time processing environments.

#### 1.8 Literature Review and Research Gaps

#### 1.8.1 Early Developments in CNN Acceleration

The evolution of CNN accelerators has been driven by the need to balance accuracy, throughput, and energy efficiency across diverse applications. Early efforts primarily relied on GPUs. While GPUs provided massive parallelism, they consumed hundreds of watts, which made them unsuitable for embedded and edge devices where energy and area are critical constraints [47,48]. Early CPU and GPU-based acceleration platforms demonstrated the potential of parallel architectures but highlighted the unsustainable overhead of general-purpose designs in power and latency-sensitive domains.