Dr. Hitesh Shrimali

| Phone : | +91-(1905)267-902 | |

|---|---|---|

| EMail : | hitesh@iitmandi.ac.in | |

| Address : | School of Computing and Electrical Engineering | |

| A10-403, North Campus | ||

| School of Computing and electrical Engineering | ||

| Kamand Campus, IIT Mandi | ||

| Mandi, Himachal Pradesh -- 175005 | ||

| India |

Bio-sketch

-

I am a Professor in the school of computing and electrical engineering. Before joining IIT Mandi, I did B.E. from Nirma Institute of Technology (Ahmedabad), M.Tech. from IIT Kharagpur and Ph.D. from IIT Delhi. My M.Tech. and Ph.D. theses were under the guidance of Prof. Amit Patra and Dr. Shouri Chatterjee respectively. After that I joined STMicroelectronics (Greater Noida) as a senior design engineer. After having 2 years of industrial experience, I worked with Università degli Studi di Milano as a post doctorate researcher, under the guidance of Prof. Valentino Liberali. During post-doctorate experience, I was also associated with INFN [Istituto Nazionale di Fisica Nucleare] Milano.

Research interests

- Design and testing of radiation hard circuits [CMOS silicon detectors]

- Analog and mixed signal VLSI design [ADCs]

- Modeling of radiation effects on analog and mixed signal circuits

- On-chip Instrumentation

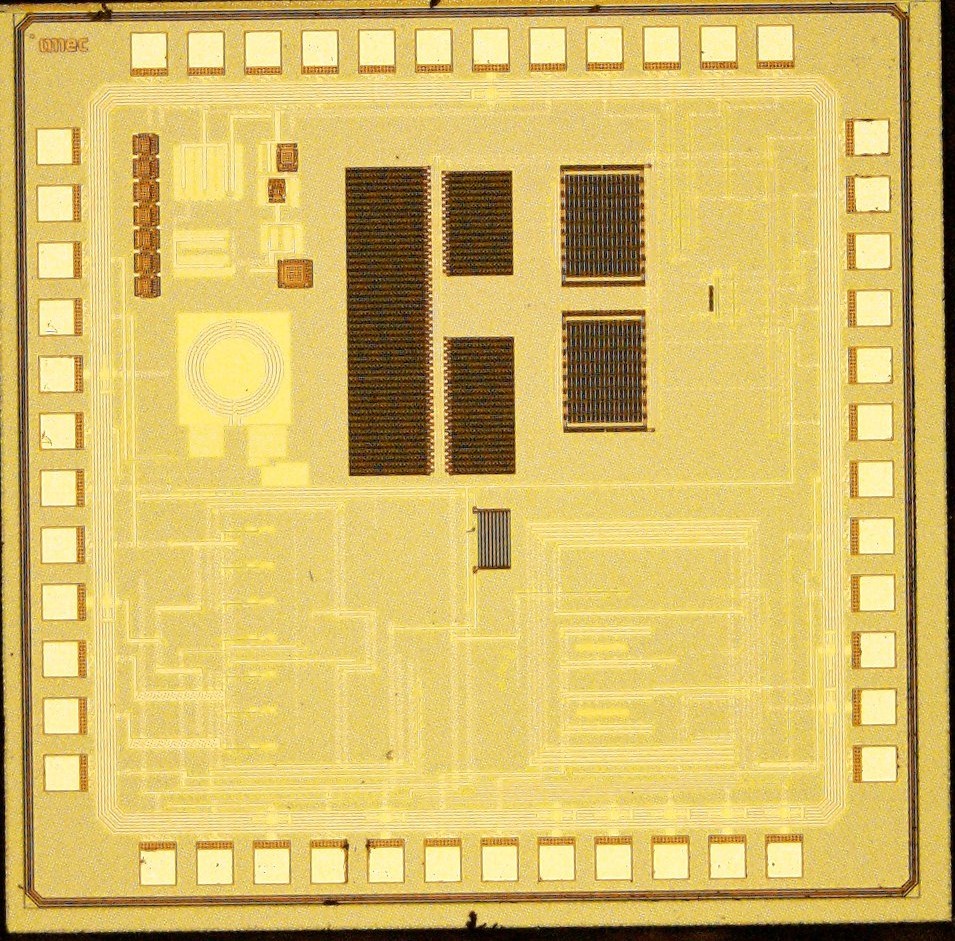

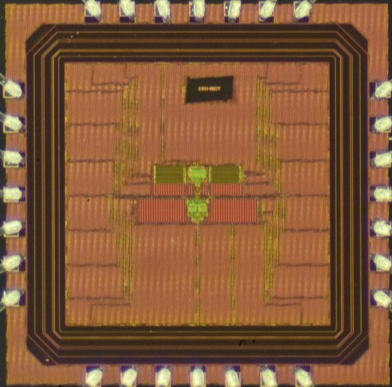

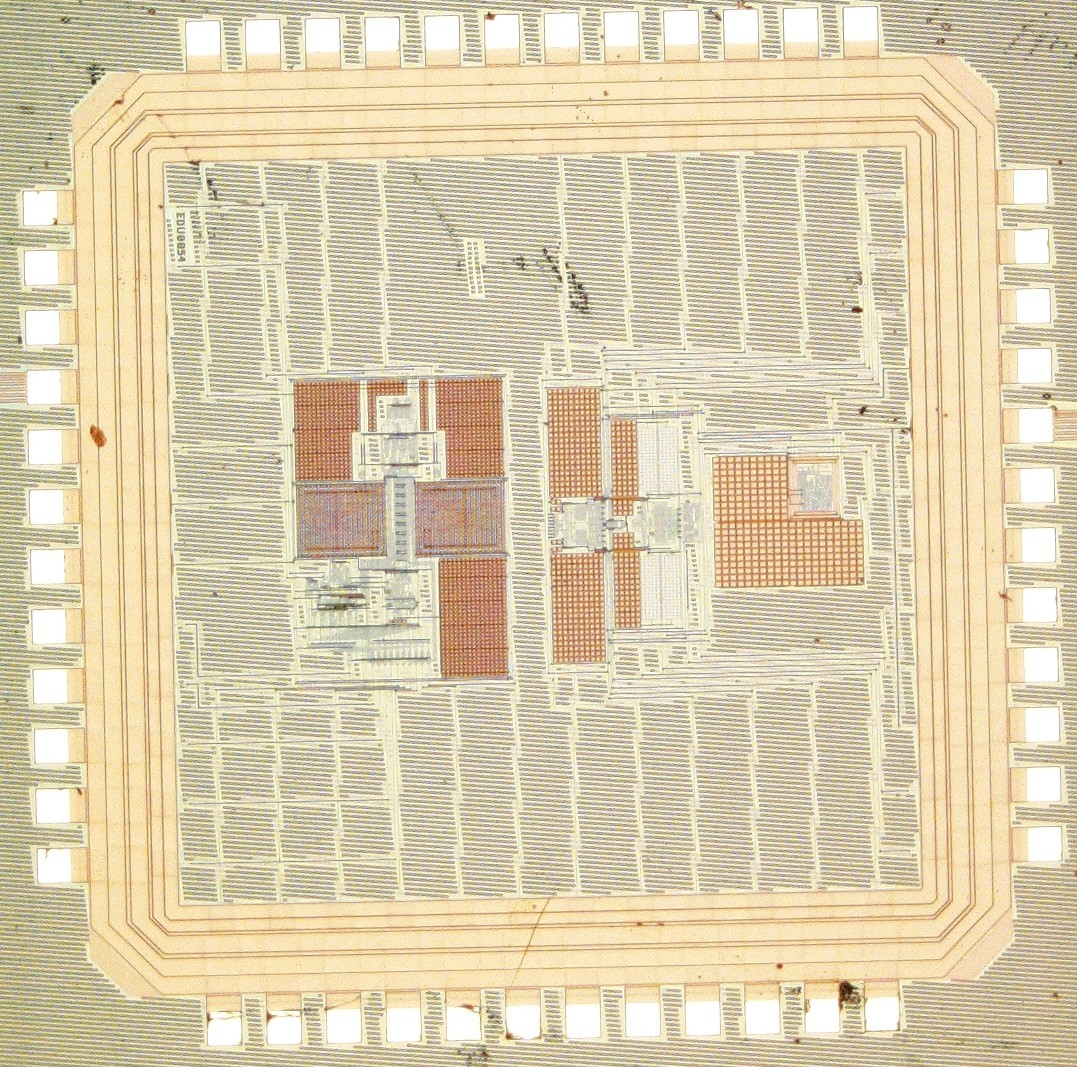

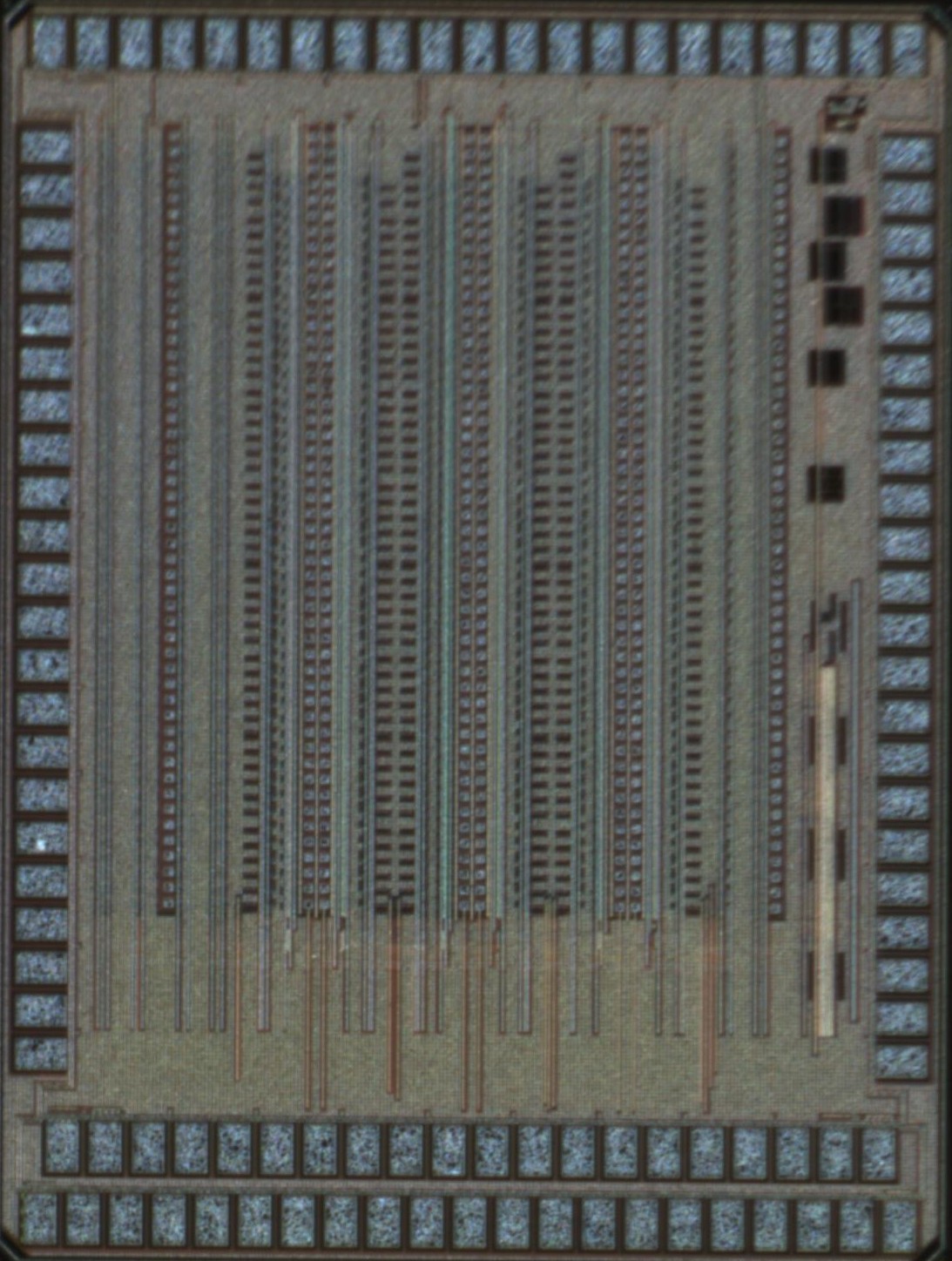

Chip tape-outs at IIT Mandi

Workshop

- BMBF funded workshop on Current Trends in Analog Circuit Designing (Sept. 25-26, 2017) Brochure

Honours and Awards

- "Young Faculty Fellow 2023" on the 14th Foundation day of IIT Mandi (February 24, 2023)

- "Excellent and Consistent Teaching Performance Combined with Contributions Towards Institute Services" on the 12th Foundation Day of IIT Mandi (February 24, 2021)

- "All-Rounder Contribution Award for the Execution of Academic and Research Activities" on the 8th Foundation Day of IIT Mandi (February 24, 2017);

- "Distinguished Alumni Award -- 2017" (Nirma University)

- "Recipient of Young Faculty Research Fellowship (YFRF)", MeitY, Govt. of India

Work Experience

- Professor: Indian Institute of Technology Mandi [Dec'24 -- Present]

- Associate Professor: Indian Institute of Technology Mandi [Jun'19 -- Dec'24]

- Assistant Professor: Indian Institute of Technology Mandi [Dec'14 -- May'19]

- Post Doctorate Researcher: Università degli Studi di Milano [Jun'13 -- Dec'14]

- Senior Design Engineer: STMicroelectronics, Greater Noida [Aug'11 - Jun'13]

On-going sponsored research projects

- Project: Ultra Small Atomic Clock for Mil-grade Applications Funding Agency: Ministry of Electronics and Technology (MeitY), Govt. of India ( Role: PI)

- Project: Learning Engineering through Activity Program (LEAP) ( Role: Co-PI)

Functional under IITM incubation cell on behalf of IIT Madras

Sanctioned Amount: 95,00,000 INR Design of High Voltage, High Resistive CMOS Silicon Particle Detector for Space Applications Funding agency: ISRO, Department of Space ( Role: PI)

Sanctioned Amount: 32,29,000/- INR

Funding Agency: Maker Bhavan Foundation, A Charitable Foundation incorporated in the USA for enabling Science Technology Engineering and Math Education and Research in India

Sanctioned Amount: 1,00,00,000 INR

Completed research projects

- Project: High Speed and Energy Efficient Hybrid Data Converters Funding Agency: Ministry of Electronics and Technology (MeitY), Govt. of India ( Role: PI)

- Project: Special Man-power Development project from Chip to system design (SMDP-C2SD) Funding Agency: Ministry of Electronics and Technology (MeitY), Govt. of India ( Role: PI)

- Project: Design and Fabrication of Interface ASIC for Vibratory Gyroscope Sensor Application Funding Agency: Indian Space Research Organization (ISRO), Govt. of India ( Role: Co-PI)

- Seed grant project Funding Agency: Indian Institute of Technology Mandi ( Role: PI)

Sanctioned Amount: 37,00,000 INR

Sanctioned Amount: 62,00,000 INR (Dec. 2015 to Nov. 2021)

Sanctioned Amount: 45,00,000 INR

Sanctioned Amount: 6,50,000 INR

Academic Administrative Experience

- Board of Directors, Catalyst, IIT Mandi (Oct'25 to present)

- Board of Governors, IIT Mandi (Jan'25 to present)

- Chairperson, Discipline Core Committee -- VLSI, SCEE, IIT Mandi (Jul'25 to present)

- Coordinator, BTech VLSI programme with NorthCap University under Centre of Continuing Education (CCE), IIT Mandi

- Dean (Students), IIT Mandi (Sept'22 to Jul'24)

- Nodal Officer, Visweswaraya PhD Scheme, MeitY (Jun. 2021 to Jun'24)

- Programme Coordinator, BTech in VLSI (Aug'23 to May'24)

- Coordinator, IP and TT Cell, IIT Mandi (Jan'22 to Oct'22)

- Chair, SCEE Publicity Committee (Mar. 2021 to Oct'22)

- Chair, Curriculum review committee for BTech (EE) (Nov'20 to Oct'22)

- Chair, Campus Return [CaRe] Committee (Oct'20 to Feb'22)

- Chair, Student Affairs Panel (SAP), IIT Mandi [Dec'19 - Sept'22]

- Chair, BTech IC-PFG, IIT Mandi (Aug'21 to Nov'22)

- Chief Election Officer, Gymkhana, IIT Mandi (Jun. 2020, and Jun. 2021)

- Course coordinator, M. Tech. (VLSI), IIT Mandi [Aug'18 - Aug'21]

- Advisor, Art Geeks, IIT Mandi [Dec'19 - Aug'21]

- Advisor, Science and Technology Councill, IIT Mandi [Apr'16-Dec'19]

- Faculty Advisor, Bech. (EE), 2015-batch, IIT Mandi [Agu'15-Jun'19]

- Co-advisor, Career and Placement Cell, IIT Mandi [Apr'16 - Jun'18]

- Faculty advisor, M. Tech. (VLSI), 2016-batch, IIT Mandi [Aug'16 - Jun'18]

- Course coordinator, M. Tech. (VLSI), IIT Mandi [Aug'16 - Sept'17]

- Event Advisor, Inter IIT Tech Meet 2016

- Advisor, Robotronics Club, IIT Mandi [Apr'16 - present]

- Advisor, Electronics Club, IIT Mandi [Mar'15 - Apr'16]

- Advisor, IEEE IES IIT Mandi student chapter (Aug'15 - Apr'16),

- Co-advisor, Cultural Club, IIT Mandi [Mar'15 - Apr'16]

Present Roles

Past Roles

Students and project staffs

PhD students (Institute Scholars)

- Shonit Mehra (Jan'26 to present)

- Manika Gupta (Aug'25 to present)

- Vivek Thakur (Aug'23 to present)

- Aastha Soni (Jan'24 to present)

- Amit Kumar (Feb'23 to present)

- Puneet Kumar Mishra (Aug'22 to present)

Part-time PhD students

- Aishwarya Kumari (Feb'21 to present) -- Cadence pvt. ltd., Bangalore, India

Master of Technology (MTech) by Research Students

- Sachin Kumar (Jan'24 to present)

Project Staff

- Sundar Murthy (MeitY, Jan'26 to present)

- Sachin Kumar (MeitY, Jan'24 to present)

- Puneet Kumar Mishra (ISRO, May'22 to Aug'22)

- Dinesh Kumar B.: Project Engineer (SMDP-C2SD, Mar'16 to Nov'21)

- Vivek Thakur: Project Assocaite (SMDP-C2SD, Oct'19 to May'21)

- Vivek Kumar: Project Associae (SMDP-C2SD, Mar'18 to Apr'19)

- Ankita Deo: Project Associate (SMDP-C2SD, Jan'17 to Dec'17)

- Sonal Chaudhary: Project Associate (SMDP-C2SD, Mar'16 to Dec'16)

Theses guidance

- Sundar Murthy (MTech in VLSI, Jan'25 to present)

- Shreyansh Hajri (MTech in VLSI, Jun'25 to present)

Graduate Students

Graduated students

- Dr. Saurabh Dhiman (May'19 to Oct'24) Postdoc at Arizona State University

- Dr. Kumar Sambhav Pandey (Feb'17 to Jul'23) Registrar at IIT Mandi (on Deputation), and Associate Professor at NIT-Hamirpur

- Dr. Dinesh Kumar B. (Feb'17-Aug'22), Greensemi, Bangalore

- Dr. Vijender Kumar Sharma (Feb'16 to Oct'21) -- Synopsys, Noida

- Dr. Shivani Sharma [Jan'15-Jul'20] -- Faculty, KIET, UPTU, India

- Dr. Ashish Joshi [Jan'15-Jun'20] -- Intel, Bangalore, India

- Dr. Indu Yadav [Feb'15-May'20] -- Siemens EDA, Noida

- Shristhi Dhangar (MTech in VLSI, Jun'24 to May'25)

- Ritika Pore (MTech in VLSI, Jun'24 to May'25)

- Sowmyasree S. (MS by Research, Sept'22 to Dec'24)

- Ajeesh (MTech in VLSI, Jun'23 to Jun'24)

- Shristhi Chauhan (MTech in VLSI, Jun'23 to Jun'24)

- Aman Nafees (MTech in VLSI, Jun'23 to Jun'24)

- Joyal Basil (MTech in VLSI, Jun'22 to Jun'23)

- Prashant Bhatt (MTech in VLSI, Jun'22 to Jun'23) -- Synopsys, Noida

- Arghyadip De (MTech in VLSI, Jun'22 to Jun'23)

- Aman Nehra (MTech in VLSI, Jun'22 to Jun'23) -- PhD at IIT Mandi

- Chaitanya Anand (MTech in VLSI, Jul'21-Jun'22) -- Texas Instruments, Bangalore

- Deepank Yadav (MTech in VLSI, Jul'21-Jun'22) -- Synopsys, Noida

- Bharath Mohan (MTech in VLSI, Jul'21-Jun'22) -- Intel, Bangalore

- Nishanth Kumar (MTech in VLSI, Jul'21-Jun'22) -- Intel, Bangalore

- Saurabh Trivedi (MTech in VLSI, Jul'21-Jun'22) -- Cadence, Bangalore

- Shubham Saxena (MTech in VLSI, Jul'20-Jun'21) -- Cadence, Noida

- Shivam (MTech in VLSI, Jul'20-Jun'21) -- Electricity Board, Haryana Govt.

- Gowtham PK (MTech in VLSI, Jul'20-Jun'21) -- Cadence, Noida

- Osho Gera (MTech in VLSI, Jul'20-Jun'21) -- NVIDIA, Bangalore

- Devrishi (MTech in VLSI, Jul'20-Jul'21) -- TI, Bangalore

- Sandeep Pareek (MTech in VLSI, May'19-Jul'20) -- Design Engineer at NXP-Semiconductor

- Saswat (MTech in VLSI, May'19-Jul'20) -- Design Engineer at Cadence, Pune

- Monu Mehta (M.Sc. in Physics, Jun'19-Jul'20)

- Adarsh Ahlawat (MTech in VLSI, May'19-Dec'20)

- Suhail Illikkal (MTech in VLSI, May'18-Jul'19) -- Design Engineer at Cadence, Noida

- Vartika Verma (MTech in VLSI, May'18-Jul'19) -- PhD at TU-Munich

- Rupal Jain (MTech in VLSI, May'18-Jun'19)

- Alvendra Singh (MTech in VLSI, May'18-Jun'19) -- Section Engineer, Indian Railways, Jaipur, India

- Sumit Kumar Pandey (MTech in VLSI, May'17-Jun'18) -- Samsung, Bangalore

- Puneet Arora (MTech in VLSI, May'17-Jun'18) -- STMicroelectronics, Greater Noida

- Tanmay Mahendra (BTech in EE, Jun'22-May'23)

- Prabhjot Singh (BTech in EE, Jun'22 to May'23)

- Sudhanshu Chauhan (BTech in EE, Jul'20-Jun'21) -- Qualcomm, Bangalore

- Srinivas Khatavkar (BTech in EE, Jul'20-21) -- Ceremorphic, Hyderabad

- Piyush Patil (BTech in EE, Jul'19-Jul'20) -- Component Engineer, Intel pvt. ltd., India

- Rachit Maheshwari (BTech in EE, Jul'19-Jul'20) -- Software Engineer, Canadian Global Informatics

- Himanshu Kumar (BTech in EE, Jul'18-Jun'19) -- OLX, Bangalore

- Nitesh Bansiwal (BTech in EE, Jul'17-Jun'18) -- Decision Analytics Associate, ZX Associates, Pune

- Anubhav Agrawal (BTech in EE, Jul'17-Jun'18) -- Associate Product Manager, OLX, Bngalore

- Anurag Rakde (BTech in EE, Jul'17-Jun'18) -- Design Engineer at Qualcomm, Hyderabad

- Niraj Singh (B.Tech. EE - 2016)

- Rohit Raghav (B.Tech. EE - 2016)

Doctor of Philosophy (PhD)

Graduate Students

Under-graduate Students

Teaching

- IC101P -- Reverse Engineering (Co-cordinator)

- IC201P -- Design Practicum (Co-coordinator)

- EE524-- Digital MOS LSI Circuits

- EE211 -- Analog Circuit Design

- EE203 -- Network Theory

- EE519P -- CMOS Digital IC Design Practicum

- EE619 -- Mixed Signal VLSI Design

- EE512 -- CMOS Analog IC design

- DP504P -- Electrical and Mechanical Workshop (for M. Sc. students)

- IC161 -- Applied Electronics

- IC161P -- Applied Electronics laboratory

On-line Video Lectures

- Digital MOS LSI Circuits (Link to YouTube Channel)

- Analog Circuit Design (Link to YouTube Channel)

- Design of CMOS Operational Amplifier (Link to YouTube Channel)

- Mixed Signal VLSI Design (Link to YouTube Channel)

Invited Lectures and Outreach Activities

- VLSI -- A Step Towards Silicon Valley, Adani University, Jan. 2, 2026.

- AICTE ATAL Online FDP on Advances in Semiconductor Technologies: From Fundamentals to AI-Driven VLSI Design and Packaging, Jan 12-17, 2026, North Cap University, Gurugram.

- Expert lecture for NCR school students, “Awareness on Semiconductors”, NSDC Delhi, Dec. 9, 2025.

- Online 10 hours of lecture series for VLSI students, “On-Chip Amplifier Design Techniques using Cadence”, Nirma University, Sept-Oct., 2025.

- An expert lecture on “VLSI Design: understanding and flow” for BTech First year, Orientation Programme, North Cap University, Sept. 2025.

- Expert lecture on “CMOS ICs: Design to Deployment”, Parul University, Gujarat, Jun’25.

- Online Faculty Development Program (FDP) on "Analog and Mixed IC Design", scheduled from May 5-16, 2025, KLEF University.

- Hands-on Workshop for graduate students, “On-Chip Operational Amplifier Design Techniques”, IIT Mandi, Apr. 11-13, 2025.

- Lecture series on “Data Converters: Specifications to the Design Architectures”, for BTech Third year ECE Students, PDEU, Gandhinagar, Gujarat, March 10-11, 2025.

- An expert lecture on “VLSI Design: Sand-to-Silicon” for BTech Third year, Orientation Programme, PDEU, Gandhinagar, Gujarat, Jan 8, 2025.

- A lecture series as a part of the FDP on “CMOS Analog IC design Techniques” for IIIT Gwalior, Jan 18-20, 2025.

- “CMOS Opamp Design Techniques”, Expert lecture series for M.Tech (VLSI and ST) Sem II students, Nirma University, Gujarat, Jan 9-10, 2025.

- AICTE Training and Learning (ATAL) Online Faculty Development Program on “AI and Digital Technologies for Sustainable Healthcare and Medical Technologies”, Nirma University, Ahmedabad, Dec’24.

- An invited lecture for the workshop "Robust and Reliable VLSI Circuits", under IEEE CASS Student Branch IIT Roorkee, supported by IEEE UP Section, April 7-9, 2023.

- Two days long Faculty Development Programme (FDP) – “VLSI – Infrastructure Requirements and Design Methodology”, IITRAM, Ahmedabad, Gujarat, Nov’24.

- Two days long workshop on Practical issues with ADC and DAC for ITI students of HP, Dec’22.

- An invited lecture on “High speed analog-to-digital conversion techniques” at IIT Delhi, Aug’22.

- Two days long Faculty Development Programme (FDP) – High Speed VLSI Design Techniques for JNGEC, HP colleges’ instructors, Jul’22.

- Two days long Faculty Development Programme (FDP) – Electronics Vertical for Himachal Pradesh Diploma colleges’ instructors, Jun’22.

- A lecture on “VLSI: Growing Opportunities with the Shrinking Technology Node” for the BTech first year Orientation of IIIT-Una, HP, Dec. 18, 2021,

- A lecture on “Design Methodology: Reverse to Forward Engineering Approach” for ATAL FDP on Design Thinking: From Insights to Viability for Engineers, Dec. 9, 2021.

- Webinar series on Analog and mixed-signal VLSI design for Vignan's Foundation for Science, Technology and Research, AP, India (Jun. 16, 2021)

- AICTE sponsored Short Term Training Program (STTP) on Mixed Signal Design approaches for Artificial Intelligence Processors for LBRCE, AP, India (March 2021)

- A lecture on, "Design and Modeling of Energy Efficient Hybrid Flash-SAR ADC", for NIT Jalandhar (Aug. 22, 2020) (Slides)

- FDP on "Trends towards Industry 4.0 in Mixeds Signal SOCs" for JUIT, Solan, HP (June 17, 2020)

- On-chip Power Delivery Networks for IIT Jodhpur (Link to the Lecture)

- High speed CMOS analog IC design for IIIT Gwalior (Apr'18)

- BJT, MOSFET and amplifiers; frequency response for QEEE phase 9 (Feb'18)

- Linear integrated circuits -- design with opamp for QEEE phase 8(Sep'17)

- Differential amplifiers for QEEE phase 7 (Mar.'17)

- BJT/MOS amplifier for QEEE phase 6 (Feb'16)

Activities

- Treasurer, IEEE CASS Delhi Chapter

- Session Chair, Signal Integrity, IEEE EDAPS 2021

- TPC Member – EDAPS; Programme and TPC Chair – VDAT 2025;

- Finance Chair – IEEE ISICAS 2024; Fellowship Chair for IEEE VDAT 2019; Organizing committee for IEEE EDAPS 2018;

- IEEE Senior member and IEEE societies’ member for NPS, CAS, IES and SSCS;

- Review Editor: Frontiers in Electronics -- Intergrated Circuits and VLSI

- Organising committee member: IEEE EDAPS` conference 2018

Granted Patents

- A. Joshi, H. Shrimali , S.K. Sharma, "Reconfigurable Reduced Switching Activity (Rsw) Mode for an Analog-To-Digital Converter", application number 201911042977, Granted in Oct. 2024Patent_Certificate

- S. Dhiman, N. Gupta, and H. Shrimali , "Method of running an unrolled binary search or multiple level search for pipeline ADC", Patent no. 520561, Application Number: 202211014204, Granted in Mar. 2024. Patent_Certificate

- U. Kunwar, P. Chaturvedi, H. Shrimali, "Fully automated electrostatic page turning technique and device for document scanning", Patent No. 534670, Application number 201911044970, granted in Apr. 2024. Patent_Certificate

Filed Patents

- V. Thakur and H. Shrimali, “Adaptive sampling based On-chip integrating type analog-to-digital converter”, Indian patent to be filed in Jan. 2026.

- P. Mishra, M. Warris, S. Mehta, R. Shrestha, H. Shrimali, “Current to Frequency based Self-Calibrated and process-voltage-temperature Insensitive Time Domain Converter”, Indian Patent filed in Oct. 2025

- S. Sugavanam, H. Shrimali, A. Khariyal, “Method of characterisation of high-speed analog-to-digital converters using asynchronous optical sampling”, Indian Patent filed in Nov. 2025.

- K.S. Pandey and H. Shrimali, “Microcell library for implementation of computational logic using digital VLSI systems”, US Patent, Application number 18878667, Filed in Jul. 2025.

- K.S. Pandey and H. Shrimali, “Data path elements for implementation of computational logic using digital VLSI systems, US Patent, Application number 18878663, filed in Jun. 2025

- M. Sakre, Z. R. Sheikh, T. Kaur, R. Nagulapalli, and H. Shrimali , "Acurrent reusable quadrature voltage-controlled oscillator (QVCO)", Application number: 202411050692, filed in Jul. 2024.

- M. Sakre, Z. R. Sheikh, R. Nagulapalli, and H. Shrimali , "A voltage-controlled oscillator (LC VCO) and method of operation thereof", Application number: 202411032951, filed in Apr. 2024.

- Dinesh B., N. Gupta, and H. Shrimali , "Adaptive hybrid analog-to-digital converter with fractional/multi bit per cycle conversion", Application number: 202013054196, filed in Dec. 2020.

- Dinesh B., N. Gupta, and H. Shrimali , "Hybrid analog-to-digital converter with fractional/multi bit per cycle conversion", application number 202011053662, filed in Dec. 2020.

Peer Reviewed International Journals

2025

- Dinesh B., N. Gupta, A. Amara, and H. Shrimali, "A 6-bit and 500 MS/s Hybrid ADC with Energy Efficient CDAC Switching Scheme" in Springer Analog Integrated Circuits and Signal Processing, Vol. 124, No. 10, May 2025, Springer_Link

2024

- S. Dhimaan, H. Shrimali, "An MDAC-Less Pipelined ADC for AI-Powered Medical Imaging Applications," in IEEE Sensors Journal, vol. 24, no. 23, pp. 39182-39194, Dec. 2024. IEEExplore_link (DOI: 10.1109/JSEN.2024.3477608.)

- S. Dhimaan, H. Shrimali, "On Minimizing Charge Injection Error Using Multi-Dummy Switches With Enhanced Linearity" in Elsevier VLSI Integration, vol. 97, pp. 102175, July 2024, Elsevier_link (DOI: 10.1016/j.vlsi.2024.102175)

2022

- V.K. Sharma, J.N. Tripathi, H. Shrimali, "Indefinite Admittance Matrix based Modelling of PSIJ in Nano-Scale CMOS I/O Drivers" in IEEE Open Access Journal of Nanotechnology, Early Access, pp. 1-10, Nov. 2022, IEEE_link (DOI: 10.1109/OJNANO.2022.3221838)

- S. Illikkal, J.N. Tripathy, V.K. Sharma, H. Shrimali, R. Achar, "Novel Observations and Physical Insight on PSIJ Behaviour in CMOS Chain-of-inverters" in IEEE Access, pp. 100172 - 100177, Sept. 2022 IEEE_link (DOI: 10.1109/ACCESS.2022.3206019) impact factor: 3.367

- S. Sharma, R. Khosla, S. Das, H. Shrimali, S.K. Sharma, "Two-Dimensional Van Der Waals Hafnium Disulfide and Zirconium Oxide-based Micro-Integrated Electrodes Transistors", IEEE TED, Early Access, 1-7, Oct. 2022 IEEE_link (DOI: 10.1109/TED.2022.3202510), impact factor:

- V.K. Sharma, J.N. Tripathi, H. Shrimali, "Design and Distortion Analysis of a Power Delivery Network in the Presence of Internal Supply Noise", in IEEE Transactions on Components, Packaging and Manufacturing Technology (TCPMT), vol. 12, issue 7, pp. 1130 - 1139, July 2022 IEEE_link (DOI: 10.1109/TCPMT.2022.3180551) impact factor: 1.738

- D. Balasubramanian, H. Shrimali,"Design and Implementation of a Second Order PLL based Frequency Synthesizer for Implantable Medical Devices", in Elsevier: Integration the VLSI Journal, Vol. 86, pp. 57-63, Sept. 2022, Elsevier_link (DOI: 10.1016/j.vlsi.2022.05.004) impact factor: 1.211.

- K.S. Pandey, H. Shrimali, "Novel VLSI Architectures and Micro-cell Libraries for Subscalar Computations", in IEEE Access, vol. 10, pp. 56985-56995, Mar. 2022 IEEE_link (DOI: 10.1109/ACCESS.2022.3157879) impact factor: 3.367.

2021

- V.K. Sharma, J.N. Tripathi, H. Shrimali, "Analysis of Power Supply Noise in AMS Circuits including the effects of Interconnects using Estimation", Elsevier AEUE - International Journal of Electronics and Communications, Vol. 139, Sept. 2021, pp. 153913, Elsevier_link (DOI: https://doi.org/10.1016/j.aeue.2021.153913) impact factor: 3.183.

- A. Joshi, H. Shrimali and S. K. Sharma, "Digitally Assisted Secondary Switch-and-Compare Technique for a SAR ADC", in IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II), vol. 68, issue 7, pp. 2317-2321, Jul. 2021, IEEExplore link (DOI: 10.1109/TCSII.2021.3053210) impact factor: 2.814

- P. Arora, J.N. Tripathi, H. Shrimali , "A Device Parameters based Analytical Modeling of Power Supply Induced Jitter in CMOS Inverters", in IEEE Transactions on Electron Devices (TED), IEEExplore link, pp. 3268-3275, vol. 68, issue 7, Jul. 2021 (DOI: 10.1109/TED.2021.3082106) impact factor: 2.913

- N. Gupta, A. Makosiej, H. Shrimali, A. Amara, A. Vladimirescu, C. Anghel, "Tunnel FET Negative-Differential-Resistance Based 1T1C Refresh-Free-DRAM, 2T1C SRAM and 3T1C DRAM", in IEEE Transactions on Nanotechnology, vol. 20, pp. 270-227, Feb. 2021, IEEExplore link (DOI: 10.1109/TNANO.2021.3061607) impact factor: 2.857.

2020

- A. Joshi, H. Shrimali and S. K. Sharma, "A Discrete-Time MOS Parametric Amplifier based Chopped Signal Demodulator" in IEEE Transactions on Very Large Scale Integration Systems (TVLSI), vol. 28, no. 11, pp. 2268-2279, Nov. 2020. IEEExplore link (DOI: 10.1109/TVLSI.2020.3015947) impact factor: 2.037

- V.K. Sharma, J. N. Tripathi, and H. Shrimali , "Deterministic Noise Analysis in Single-Stage Amplifiers by Extension of Indefinite Admittance Matrix", in IEEE Open Journal of Circuits and Systems (OJCAS), vol. 1, pp. 124-139, 2020. IEEExplore_link (DOI: 10.1109/OJCAS.2020.3016017)

- A. Joshi, H. Shrimali and S. K. Sharma, "Reduced Switching Mode for a SAR ADC: Analysis and Design of a SAR A-to-D Algorithm with Periodic Stand-by Mode Circuit Components" in IET Circuits, Devices & Systems, Vol. 14, issue 5, Aug. 2020, pp. 686-694. IEEExplore link (DOI: 10.1049/iet-cds.2019.0224) impact factor: 1.277

- Dinesh B., S.K. Pandey, N. Gupta and H. Shrimali "Design of hybrid flash-SAR ADC using an inverter based comparator in 28 nm CMOS" in Microelectronics Journal, vol. 95, Jan. 2020, 104666.Elsevier_Link (DOI: 10.1016/j.mejo.2019.104666) impact factor: 1.405

2019

- J.N. Tripathi, S. Illikkal, H. Shrimali, R. Achar, "A Thomas Algorithm based Generic Approach for Modeling of Power Supply Induced Jitter in CMOS Buffers", in IEEE Access, vol. 7, Jul. 2019, pp. 125240-125252.IEEExplore_link (DOI: 10.1109/ACCESS.2019.2937922) impact factor: 3.745

- I. Yadav, H. Shrimali , "Noise and Crosstalk Models of the Particle Detector with Zero-Pole Transformation Charge Sensitive Amplifier", in Elsevier Nuclear Instruments and Methods in Physics Research: A, Vol. 937, 1 Sept. 2019, pp. 107-116. Elsevier_Link (DOI: 10.1016/j.nima.2019.05.037) impact factor: 1.265

- S. Sharma, S. Das, R. Khosla, H. Shrimali and S. K. Sharma, "Realization and Performance Analysis of Facile Processed µ-IDE based multi-layer HfS2/HfO2 Transistors" in IEEE Transaction on Electron Devices, vol. 66, no. 7, Jul. 2019, pp. 3236-3241. IEEExplore_link (DOI: 10.1109/TED.2019.2917323) impact factor: 2.913

- S. Sharma, S. Das, R. Khosla, H. Shrimali and S. K. Sharma, "Highly UV sensitive Sn Nanoparticles blended with polyaniline onto Micro-Interdigitated Electrode Array for UV-C detection applications" in Journal of Materials Science: Materials in Electronics, Vol. 30, Issue 8, Apr. 2019, pp 7534-7542. Read Paper (DOI: 10.1007/s10854-019-01067-9) impact factor: 2.220

2018

- J.N. Tripathi, P. Arora, H. Shrimali and R. Achar, "Efficient Jitter Analysis for a Chain of CMOS Inverters", in IEEE Transactions on Electromagnetic Compatibility, vol. 10, Oct. 2018, pp. 1-11. IEEExplore_link (DOI: 10.1109/TEMC.2018.2878354)impact factor: 1.882

- J.N. Tripathi, V. Sharma and H. Shrimali , "A Review on Power Supply Induced Jitter", in IEEE Transactions on Components, Packaging and Manufacturing Technology (TCPMT), vol. 9, issue 3, Sept. 2018, pp. 511 - 524. IEEExplore_link (DOI: 10.1109/TCPMT.2018.2872608) impact factor: 1.889

- S. Sharma, S. Das, H. Shrimali and S. K. Sharma, "High-Performance CSA-PANI based Organic Phototransistor by Elastomer Gratings" in Elsevier Journal of Organic Electronics, Vol. 57, pp. 14-20, Jun. 2018, pp. 14-20. ElsevierLink (DOI: 10.1016/j.orgel.2018.02.031) impact factor: 3.31

- I. Yadav, H. Shrimali , A.Andreazza, V. Liberali, "Analytical Expressions for Noise and Crosstalk Voltages of the High Energy Silicon Particle Detector", Journal of Instrumentation, Institute of Physics (IOP) science, vol. 13, Jan. 2018, pg. C01019. IOP_Link (DOI: 10.1088/1748-0221/13/01/c01019) impact factor: 1.454

2017

- S. Sharma, R. Khosla, D. Deva, H. Shrimali and S. K. Sharma, "Fluorine-chlorine co-doped TiO2/CSA doped polyaniline based high performance inorganic/organic hybrid heterostructure for UV photodetection applications" in Elsevier Sensors and Actuators: A. physical, vol. 261, Jul. 2017, pp. 94-102. Elsevier_link (DOI: 10.1016/j.sna.2017.04.043) impact factor: 2.904

- A. Joshi, H. Shrimali and S. K. Sharma, "A Systematic Design Approach for a Gain Boosted Telescopic OTA with Cross Coupled Capacitor" in IET Circuits, Devices and Systems, Vol. 11, issue 3, Jun. 2017, pp. 225 - 231. IEEExplore_link (DOI: 10.1049/iet-cds.2016.0448) impact factor: 1.277

2016

- A. Andreazza, A. Castoldi, V. Ceriale, G. Chiodini, M. Citterio, G. Darbo, G. Gariano, A. Gaudiello, C. Guazzoni, A. Joshi, V. Liberali, S. Passadore, F. Ragusa, E. Ruscino, C. Sbarra, A. Sidoti, H. Shrimali, A. Stabile, I. Yadav and E. Zaffaroni, "HV-CMOS detectors in BCD8 technology", Journal of Instrumentation, Institute of Physics (IOP) science, vol. 11, Nov. 2016, pp. C11038.IOP_Link (DOI: 10.1088/1748-0221/11/11/c11038) impact factor: 1.454

2015

- H. Shrimali and Shouri Chatterjee, "A Technique to Linearize the Discrete-Time Parametric Amplifier and its Variants," Microelectronics Journal, vol. 46, no. 11, Nov 2015, pp. 1033-1038.Elsevier_Link (DOI: 10.1016/j.mejo.2015.08.013) impact factor: 1.405

2014

- H. Shrimali and V. Liberali, "Parametric Amplifier based Dynamic clocked Comparator," Solid State Electronics Journal, vol. 101, Nov. 2014, pp. 85-89. Elsevier_Link (DOI: 10.1016/j.sse.2014.06.043) impact factor: 1.437

- A. Camplani, S. Shojaii, H. Shrimali, V Liberali, “CMOS IC Radiation Hardening by Design”, in FACTA Universitatis, Journal series: Electronics and Energetics Vol. 27, no. 2, June 2014, pp.251–258. Read Paper (DOI: 10.2298/FUEE1402251C) impact factor: 0.515

2011

- H. Shrimali and S. Chatterjee, "Distortion analysis of a three terminal MOS-based discrete time parametric amplifier," in IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 58 , No. 12, Dec. 2011, pp. 902-905. IEEExplore_link (DOI: 10.1109/TCSII.2011.2172710) impact factor: 2.814

Peer Reviewed International Conferences

2025

- S. Kumar and H. Shrimali, "Current Bleeder-Based Mixer with -8.4 dB FoM, 10 dB NF, 18.5 dB Conversion Gain at 4.6 GHz," IEEE International Conference on Electronics, Circuits and Systems (ICECS), Nov. 2025.

- P. Mishra, M. Warris, S. Mehta, R. Shrestha, H. Shrimali, “Design of a Current-to-Frequency Converter with 0.18 pJ and 334 Hz/nA in 180 nm BCD-SOI”, in IEEE PRIME, Sept. 2025.

2024

- A. Yaseen NJ, H. Shrimali, D. Das, "A 66-dBΩ 5-GHz and 44.88-√Hz/(pA·pW) Inductorless Transimpedance Amplifier in 65-nm CMOS" in IEEE MIXDES, Jun. 2024.

- S. Dhimaan, H. Shrimali, "A 12.7 Bit Accurate and 5.3 nJ·μV2·ns Comparator with Dynamic-cum-Body Bias Technique in SOI" in IEEE ISCAS, May. 2024.

- S. Sowmyasree, H. Shrimali, "An On-chip Thermoelectric Cooler Controller With Improved Driving Current of 2A at 0.5 Ω Load" in IEEE VLSI Design conference, Jan. 2024. IEEExplorer link (DOI: 10.1109/VLSID60093.2024.00027)

2023

- S. Sowmyasree, H. Shrimali, "Fully Monolithic 1A Thermoelectric Cooler Controller with 90% Efficiency" in IEEE International Conference on Electronics, Circuits and Systems (ICECS), Dec. 2023. IEEExplorer link (DOI: 10.1109/ICECS58634.2023.10382722)

- S. Sowmyasree, H. Shrimali, "A Low Noise Bandgap Reference with 0.89 V Vref , 0.88 µV rms noise and 80 dB of PSRR " in IEEE VLSI Design conference,pp. 53-58, Jan. 2023. IEEExplorer link (DOI: 10.1109/VLSID57277.2023.00025)

2021

- G.P. Kalarikkal, R. Goel, H. Shrimali, "Design of CMOS Device Process Sensor in 28 nm FD-SOI with 2 % of Frequency Spread", in the IEEE ICECS, Dubai, UAE, pp. 1-6, IEEExplorer link (DOI: 10.1109/ICECS53924.2021.9665465).

- N. Gupta,H. Shrimali, A. Makosiej, A. Vladimirescu, A. Amara, "Energy Efficient Comparator-Less Current-Mode TFET-CMOS Co-Integrated Scalable Flash ADC", in IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Aug. 2021, pp. 297-300, IEEExplorer link (DOI: 10.1109/MWSCAS47672.2021.9531911).

- P. Arora, J.N. Tripathi, H. Shrimali, "Analytical Modeling of Jitter in CMOS Inverters Due to Periodic Fluctuations in Power Supply", in IEEE NEWCAS, June 2021, pp. 1-4, IEEExplorer link (DOI: 10.1109/NEWCAS50681.2021.9462738).

- Dinesh B., H. Shrimali, N. Nallam, "A Low-Power Quadrature LC− Oscillator Using Core-and-Coupling Current-Reuse", in IEEE ISCAS, pp. 1-5, May 2021, IEEExplorer link (DOI: 10.1109/ISCAS51556.2021.9401110).

2020

- V.K. Sharma, J.N. Tripathi, H. Shrimali, "An Inspection Based Method to Analyse Deterministic Noise in N-port Circuits", in the IEEE EPEPS 2020, pp-1-3, Oct. 2020.IEEExplorer link (DOI: 10.1109/EPEPS48591.2020.9231394)

- V.K. Sharma, J.N. Tripathi, H. Shrimali, "A Generalized Approach for Analyzing the Impact of Supply Noise in MOS Amplifiers", in the IEEE SPI 2020, pp- 1-4, May. 2020.IEEExplore link (DOI: 10.1109/SPI48784.2020.9218158)

- S. Dhiman, V.K. Sharma, H. Shrimali,"Design and Analysis of Low PSIJ, Energy Efficient Bootstrapped Driver for Space Application", in the IEEE ISCAS, Oct. 2020, Seville, Spain.IEEExplore link (DOI:10.1109/ISCAS45731.2020.9181133)

2019

- I. Yadav, A. Joshi, E. Ruscino, V. Liberali, A.Andrezza, H. Shrimali, "Design of HV-CMOS Detectors in BCD Technology with Noise and Crosstalk Measurements", in the IEEE ICECS, Nov. 2019, Genova, Italy. IEEExplore link (DOI: 10.1109/ICECS46596.2019.8965094)

- S. Dhiman, I. Yadav, H. Shrimali,"Energy Efficient Bootstrapped Driver for a Particle Detector in 180 nm SOI Technology", in the Asia Pacific Conference on Circuits and Systems (APCCAS) 2019, Bangkok, Thailand. IEEExplore link (DOI: 10.1109/APCCAS47518.2019.8953075)

- K. S. Pandey, Dinesh B., N. Goel, H. Shrimali , "An Ultra-Fast Parallel Prefix Adder" in the IEEE Computer Arithmetic (Arith), Kyoto, Japan, Jun. 10-12, 2019. IEEExplore link (DOI: 10.1109/ARITH.2019.00034)

- S. Illikkal, J. Tripathi, H. Shrimali , "Jitter Estimation in a CMOS Tapered Buffer for an Application of Clock Distribution Network" in the IEEE APEMC, Sapporo, Japan, Jun. 3-7, 2019. IEEExplore link (DOI: 10.23919/EMCTokyo.2019.8893857)

- V.K. Sharma, Dinesh B., S. Illikkal, J.N. Tripathi, N. Gupta, H. Shrimali, "Analysis of Timing Error Due to Supply and Substrate Noise in an Inverter Based High-Speed Comparator", in the IEEE ISCAS, Sapporo, Japan, May. 2019. IEEExplore link (DOI: 10.1109/ISCAS.2019.8702313)

- Dinesh B., N. Gupta, H. Shrimali, "A 6-Bit 29.56 fJ/conv-Step, Voltage Scalable Flash-SAR Hybrid ADC in 28 nm CMOS", in the IEEE ISCAS, Sapporo, Japan, May. 2019. IEEExplore link (DOI: 10.1109/ISCAS.2019.8702482)

- S. Illikkal, J. Tripathi, H. Shrimali , "Analyzing the Impact of Various Deterministic Noise Sources on Jitter in a CMOS Inverter" in the IEEE International Conference on Signal Processing & Integrated Networks, SPIN 2019, Delhi, Mar. 7-8, 2019.IEEExplore link (DOI: 10.1109/SPIN.2019.8711770)

- I. Yadav, A. Joshi, E. Ruscino, A. Andreazza, V. Liberali, H. Shrimali , "Design of a Charge Sensitive Amplifier for Silicon Particle Detector in BCD 180 nm Process" in the International Conference on VLSI Design (VLSID), Delhi, India, Jan. 5-9, 2019. IEEExplore link (DOI: 10.1109/VLSID.2019.00126)

2018

- V.Sharma, J. Tripathi, H. Shrimali , "Extension of EMPSIJ Method for Substrate Noise Induced Jitter: an Inverter Case Study" in the IEEE Electrical Design of Advanced Packaging and Systems (EDAPS) Symposium, Chandigarh, India, Dec. 16-18, 2018. IEEExplore link (DOI: 10.1109/EDAPS.2018.8680885)

- V.Sharma, J. Tripathi, H. Shrimali , "A Quick Assessment of Nonlinearity in Power Delivery Networks" in the IEEE Electrical Design of Advanced Packaging and Systems (EDAPS) Symposium, Chandigarh, India, Dec. 16-18, 2018. IEEExplore link (DOI: 10.1109/EDAPS.2018.8680881)

- A. Deo, S.K. Pandey, A. Joshi, S.K. Sharma, H. Shrimali, "Design of a Third Order Butterworth Gm-C Filter for EEG Signal Detection Application", in IEEE International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Gdynia, Poland, Jun. 21-23, 2018. IEEExplore link (DOI: 10.23919/MIXDES.2018.8436689)

- A. Joshi, H. Shrimali , S.K. Sharma, "The Capacitively Coupled Chopper Stabilized Amplifier With a DTPA based Demodulator", in IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, May. 27-30, 2018, pp-1-5. IEEExplore link (DOI: 10.1109/ISCAS.2018.8351188)

2017

- H. Shrimali , V.Sharma, J. Tripathi, R. Malik, "Nonlinear Modeling and Analysis of Buck Converter using Volterra Series" in IEEE International Conference on Electronics Circuits and Systems (ICECS), Batumi, Georgia, Dec. 5-8, 2017, pp-222-226. IEEExplore link (DOI: 10.1109/ICECS.2017.8292119)

- V.Sharma, J. Tripathi, H. Shrimali , R. Malik, "The Harmonics Impact Study of a DC-DC Buck Converter through a Power Delivery Network" in the IEEE Electrical Design of Advanced Packaging and Systems (EDAPS) Symposium, Hangzhou, China, Dec. 14-16, 2017, pp-1-3. IEEExplore link (DOI: 10.1109/EDAPS.2017.8276952)

- Dinesh Kumar B., H. Shrimali , "Design of a 520 μW, –141 dBc/Hz and 450 MHz Frequency Synthesizer using Low Power and Low Phase Noise Current Reuse VCO" in IEEE TENCON, Penang, Malaysia, Nov 5-8, 2017, pp-2937-2912. IEEExplore link (DOI: 10.1109/TENCON.2017.8228365)

- V.Sharma, H. Shrimali , J. Tripathi, R. Malik, "Distortion Analysis for a DC-DC Buck Converter" in the International SoC design conference (ISOCC), Seoul, Korea, Nov 5-8, 2017, pp-212-213 (Got the ISOCC Best Paper Award). IEEExplore link (DOI: 10.1109/ISOCC.2017.8368857)

2016

- A. Andreazza, A. Castoldi, V. Ceriale, G. Chiodini, M. Citterio, G. Darbo, G. Gariano, A. Gaudiello, C. Guazzoni, V. Liberali, S. Passadore, F. Ragusa, A. Rovani, E. Ruscino, C. Sbarra, H. Shrimali and E. Zaffaroni, "HV-CMOS detectors for High Energy Physics: characterization of BCD8 technology and controlled hybridization technique" in IEEE Nuclear Science Symposium 2016 (NSS), Oct. 29- Nov. 6, 2016, pp-1-3. IEEExplore link (DOI: 10.1109/NSSMIC.2016.8069868)

- A. Joshi, I. Yadav, S. Sharma, H. Shrimali , "The Pole-zero Doublet: a Cascode Operational Amplifier with Cross Coupled Capacitor" in IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Abu Dhabi (UAE), Oct. 16-19, 2016, pp-1-4. IEEExplore link (DOI: 10.1109/MWSCAS.2016.7869985)

- J. Tripathi, V. Sharma, H. Advani, P. Singh, H. Shrimali and R. Malik, "An Analysis of Power Supply Induced Jitter for a Voltage Mode Driver in High Speed Serial Links", in IEEE Workshop on Signal and Power Integrity (SPI), Turin, Italy, May 8-11, 2016, pp-1-4. IEEExplore link (DOI: 10.1109/SaPIW.2016.7496259)

2014

- H. Shrimali and V. Liberali, "The Start-up Circuit for a Low Voltage Bandgap Reference", in IEEE International Conference on Electronics Circuits and Systems (ICECS), Marseille, France, Dec 7-10, 2014, pp-92-95. IEEExplore link (DOI: 10.1109/ICECS.2014.7049929)

- H. Shrimali and V. Liberali, "A Threshold Voltage Modeling for A Spacer-Trapping Memory Cell Using Verilog-A," in Workshop on Compact Modeling (WCM), Washington, USA, June 16-18, 2014, pp-529-532.Paper_link (ISBN: 978-1-4822-5827-1)

2013

- H. Shrimali, “Discrete Time Parametric Amplifier based Dynamic clocked Comparator” in International Semiconductor Device Research Symposium (ISDRS) 2013, Bethesda (Maryland), Dec. 10-13, 2013.Paper_link

2011

- H. Shrimali and S. Chatterjee, "Third order harmonic cancellation technique for a parametric amplifier," in IEEE International Symposium on Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, May 15-18, 2011, pp. 1880–1883. IEEExplore link (DOI: 10.1109/ISCAS.2011.5937954)

- H. Shrimali and S. Chatterjee, "11 GHz UGBW Op-amp with feed-forward compensation technique," in IEEE International Symposium on Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, May 15-18, 2011, pp. 17–20. IEEExplore link (DOI: 10.1109/ISCAS.2011.5937490)

Posters

- V.K. Sharma, J.N. Tripathi, and H. Shrimali, "Modeling and analysis of power delivery network using Volterra series" Poster presented at PhD Forum, VLSI-SOC 2018, Verona, Italy, 2018.

- H. Shrimali , A. Joshi, E. Ruscino, I. Yadav, S. K. Sharma, A. Andreazza, V. Liberali, "Design of a Charge Sensitive Amplifier for Particle Detection Application in BCD 180~nm Technology" in the International Workshops on Radiation Imaging Detectors (iWoRid), Krakow, Poland, July 2-6, 2017.

- I. Yadav, H. Shrimali , A.Andreazza, V. Liberali, "Analytical Expressions for Noise and Crosstalk Voltages of the High Energy Silicon Particle Detector" in the International Workshops on Radiation Imaging Detectors (iWoRid), Krakow, Poland, July 2-6, 2017.

- A. Andreazza, A. Castoldi, V. Ceriale, G. Chiodini, M. Citterio, G. Darbo, G. Gariano, A. Gaudiello, C. Guazzoni, V. Liberali, S. Passadore, F. Ragusa, A. Rovani, E. Ruscino, C. Sbarra, H. Shrimali and E. Zaffaroni, "Characterization of HV-CMOS detectors in BCD8 technology and of a controlled hybridization technique", in the International Workshop on Vertex Detectors, Vertex 2016, Isola d'Elba, Italy, Sept. 25-30, 2016.

- A. Andreazza, A. Castoldi, G. Chiodini, M. Citterio, G. Darbo, G. Gariano, A. Gaudiello, C. Guazzoni, A. Joshi, V. Liberali, S. Passadore, F. Ragusa, E. Ruscino, C. Sbarra, A. Sidoti, H. Shrimali, I. Yadav and E. Zaffaroni, "HV-CMOS detectors in BCD8 technology", in the International Workshop on Semiconductor Pixel Detectors for Particles and Imaging (Pixel 2016), Sestri Levante, Italy, Sept. 5-9, 2016.

- A. Andreazza, A. Castoldi, G. Chiodini, M. Citterio, G. Darbo, G. Gariano, A. Gaudiello, C. Guazzoni, V. Liberali, S. Passadore, F. Ragusa, A. Rovani, E. Ruscino, C. Sbarra, A. Sidoti, H. Shrimali and E. Zaffaroni, "HV-CMOS detectors for High Energy Physics: characterization of BCD8 technology and controlled hybridization technique", in the International Workshops on Radiation Imaging Detectors (iWoRid), Barcelona, Spain, July 3-7, 2016.

- H. Shrimali, "Third order harmonic cancellation technique for a parametric amplifier," Poster presented on National science day, Indian Institute of Technology Delhi, Feb 28, 2011.

- H. Shrimali, "Ultra low power high speed onchip digital storage oscilloscope," Poster presented on National science day, Indian Institute of Technology Delhi, Feb 29, 2008.

.